Basic timers (TIM6/7) RM0402

602/1163 RM0402 Rev 6

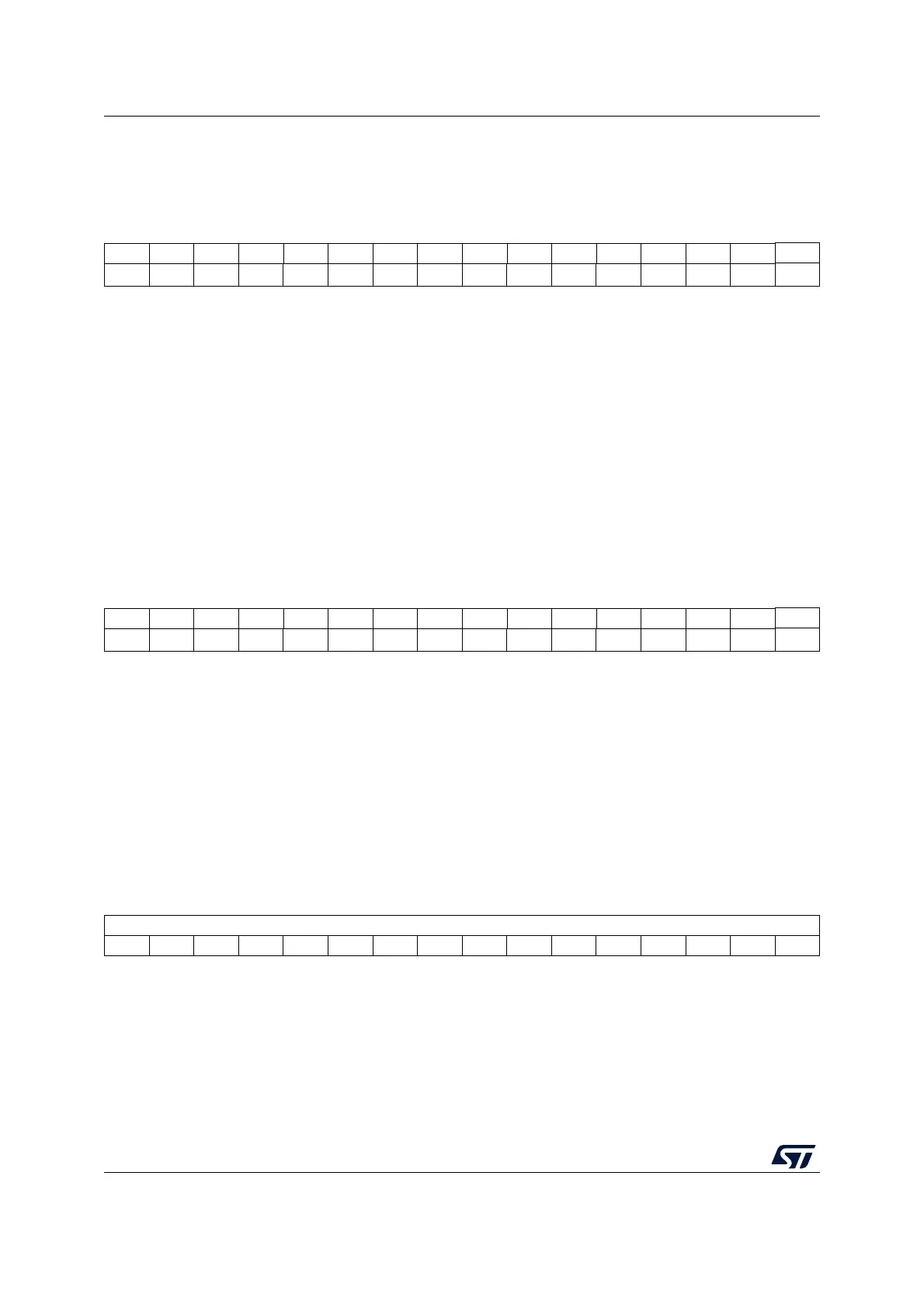

19.4.4 TIM6/7 status register (TIMx_SR)

Address offset: 0x10

Reset value: 0x0000

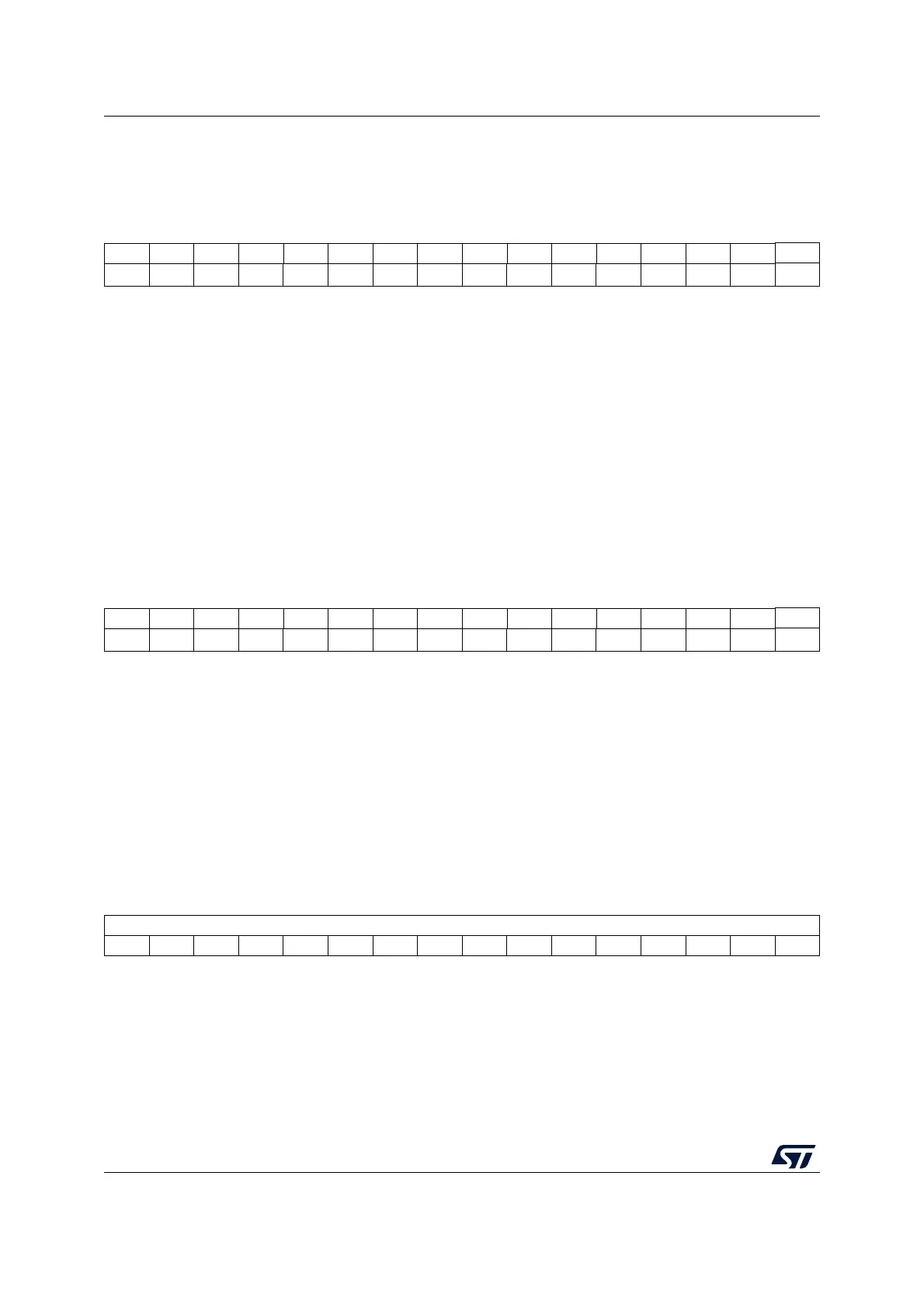

19.4.5 TIM6/7 event generation register (TIMx_EGR)

Address offset: 0x14

Reset value: 0x0000

19.4.6 TIM6/7 counter (TIMx_CNT)

Address offset: 0x24

Reset value: 0x0000

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. UIF

rc_w0

Bits 15:1 Reserved, must be kept at reset value.

Bit 0 UIF: Update interrupt flag

This bit is set by hardware on an update event. It is cleared by software.

0: No update occurred.

1: Update interrupt pending. This bit is set by hardware when the registers are updated:

– At overflow or underflow regarding the repetition counter value and if UDIS = 0 in the

TIMx_CR1 register.

– When CNT is reinitialized by software using the UG bit in the TIMx_EGR register, if URS = 0

and UDIS = 0 in the TIMx_CR1 register.

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. UG

w

Bits 15:1 Reserved, must be kept at reset value.

Bit 0 UG: Update generation

This bit can be set by software, it is automatically cleared by hardware.

0: No action.

1: Re-initializes the timer counter and generates an update of the registers. Note that the

prescaler counter is cleared too (but the prescaler ratio is not affected).

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

CNT[15:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 15:0 CNT[15:0]: Counter value

Loading...

Loading...