Power controller (PWR) RM0402

98/1163 RM0402 Rev 6

Entering Stop mode

The Stop mode is entered according to Section : Entering low-power mode, when the

SLEEPDEEP bit in the Cortex

®

-M4 with FPU System Control register is set.

Refer to Table 21 for details on how to enter the Stop mode.

To further reduce power consumption in Stop mode, the internal voltage regulator can be put

in low-power mode. This is configured by the LPDS bit of the

PWR power control register

(PWR_CR).

If Flash memory programming is ongoing, the Stop mode entry is delayed until the memory

access is finished.

If an access to the APB domain is ongoing, The Stop mode entry is delayed until the APB

access is finished.

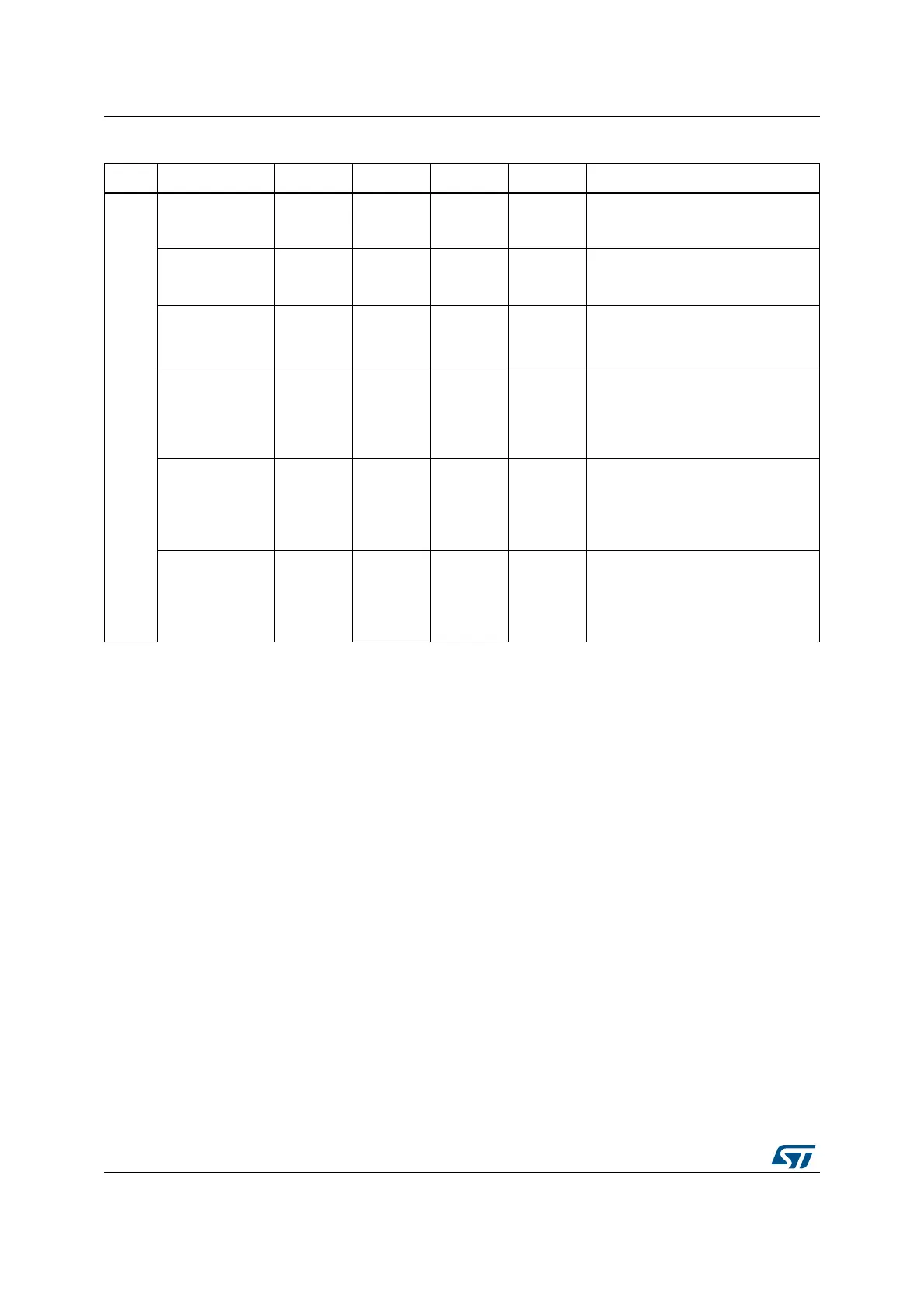

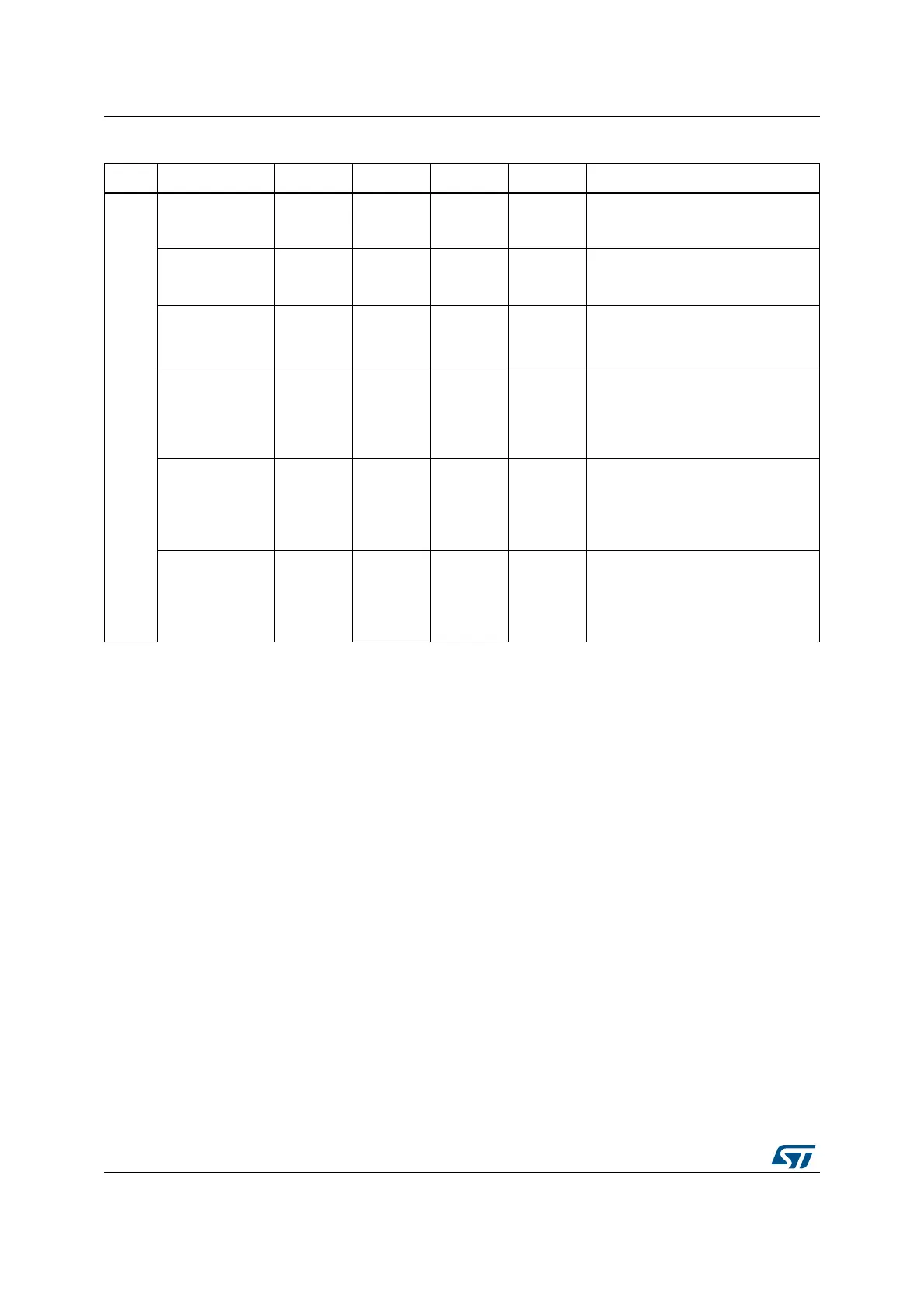

Table 20. Stop operating modes

Stop mode MRLV bit LPLV bit FPDS bit LPDS bit Wakeup latency

Normal mode

STOP MR 0 - 0 0 HSI RC startup time

STOP MRFPD 0 - 1 0

HSI RC startup time +

Flash wakeup time from Deep

Power Down mode

STOP LP 0 0 0 1

HSI RC startup time +

regulator wakeup time from LP

mode

STOP LPFPD - 0 1 1

HSI RC startup time +

Flash wakeup time from Deep

Power Down mode +

regulator wakeup time from LP

mode

STOP MRLV 1 - - 0

HSI RC startup time +

Flash wakeup time from Deep

Power Down mode +

Main regulator from low voltage

mode

STOP LPLV-1-1

HSI RC startup time +

Flash wakeup time from Deep

Power Down mode +

regulator wakeup time from Low

Voltage LP mode

Loading...

Loading...