RM0402 Rev 6 919/1163

RM0402 Secure digital input/output interface (SDIO)

921

27.8.15 SDIO data FIFO register (SDIO_FIFO)

Address offset: 0x80

Reset value: 0x0000 0000

The receive and transmit FIFOs can be read or written as 32-bit wide registers. The FIFOs

contain 32 entries on 32 sequential addresses. This allows the CPU to use its load and store

multiple operands to read from/write to the FIFO.

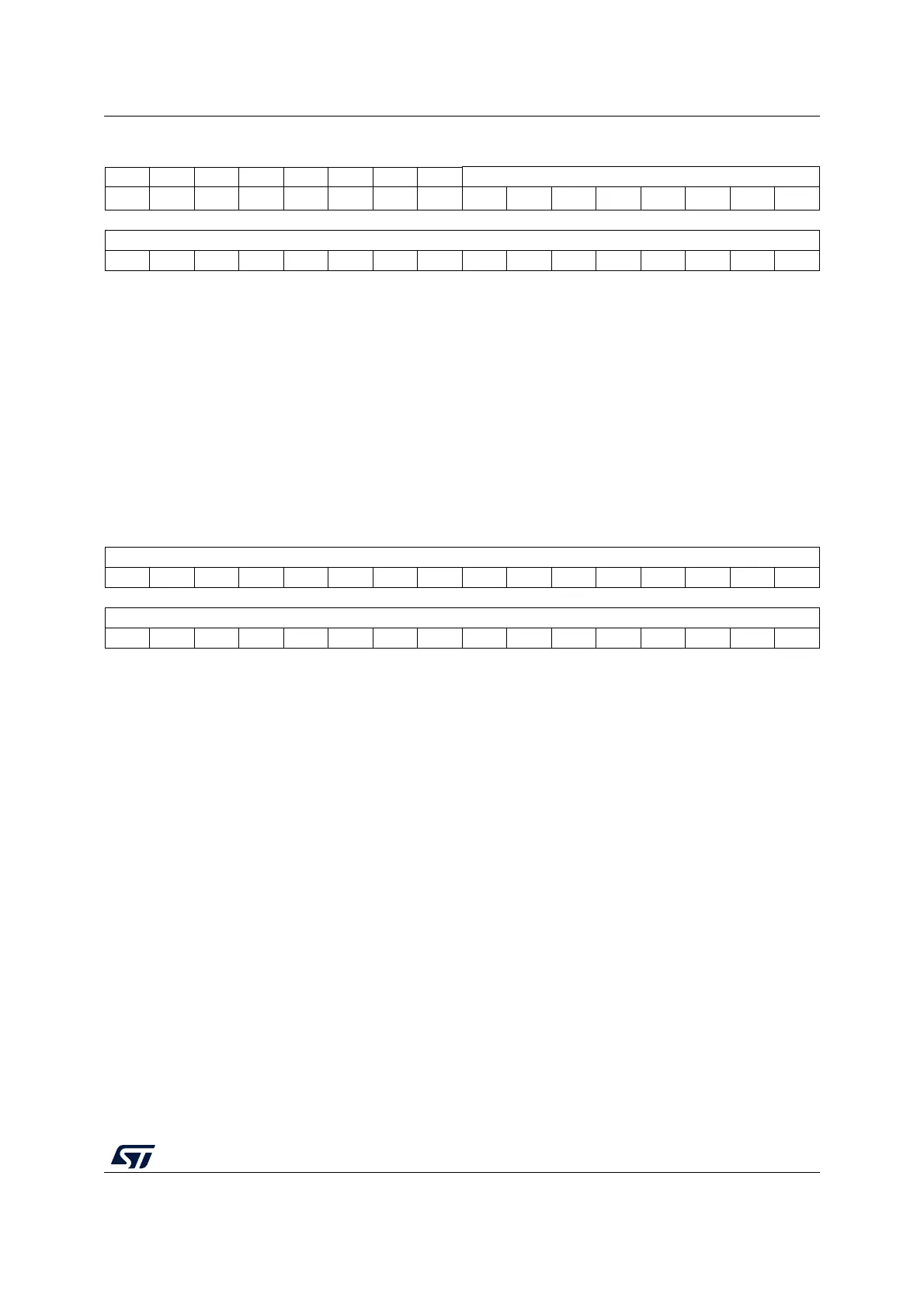

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. FIFOCOUNT[23:16]

rrrrrrrr

1514131211109876543210

FIFOCOUNT[15:0]

rrrrrrrrrrrrrrrr

Bits 31:24 Reserved, must be kept at reset value.

Bits 23:0 FIFOCOUNT: Remaining number of words to be written to or read from the FIFO.

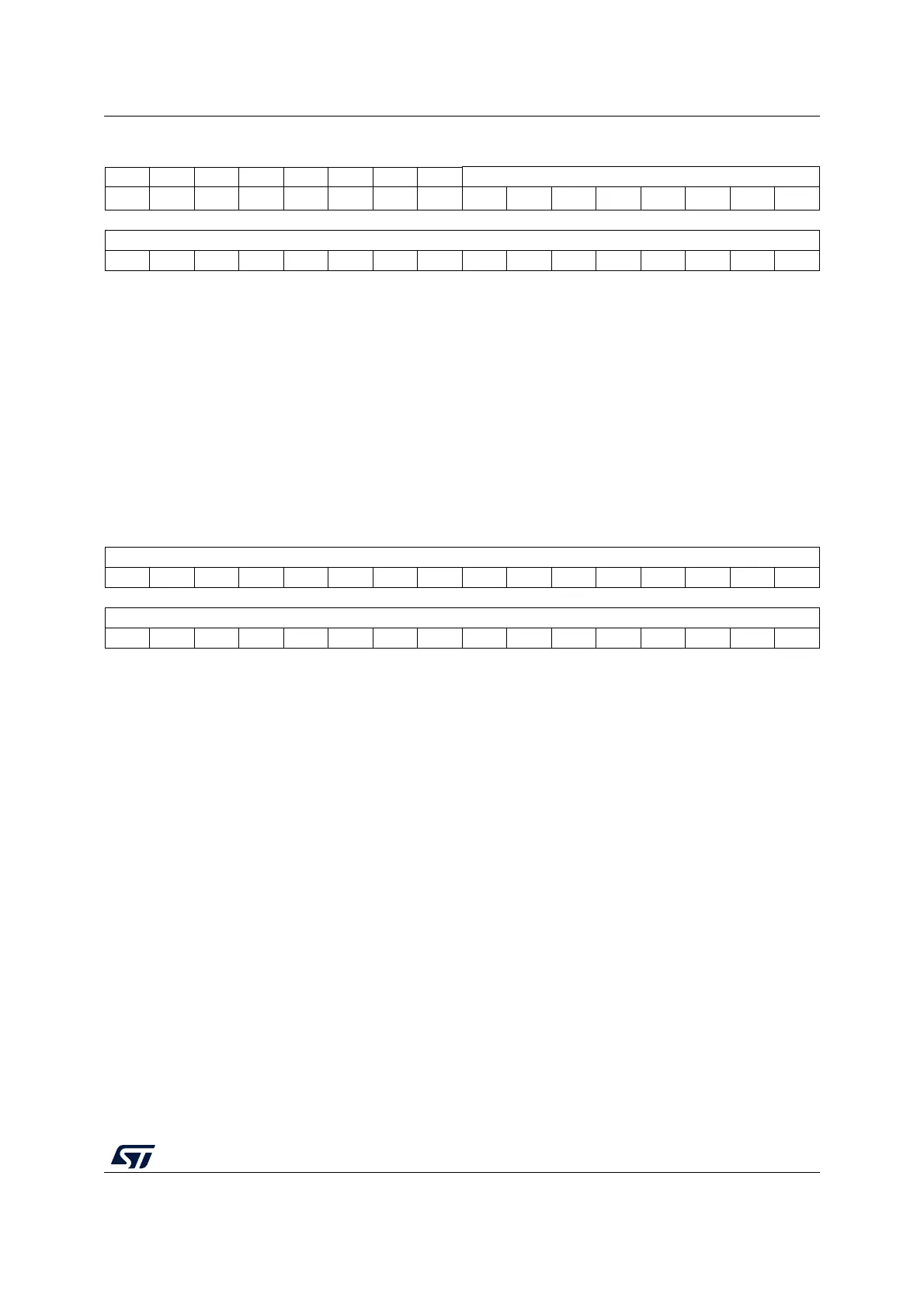

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

FIF0Data[31:16]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

1514131211109876543210

FIF0Data[15:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

bits 31:0 FIFOData: Receive and transmit FIFO data

The FIFO data occupies 32 entries of 32-bit words, from address:

SDIO base + 0x080 to SDIO base + 0xFC.

Loading...

Loading...