RM0402 Rev 6 359/1163

RM0402 Digital filter for sigma delta modulators (DFSDM)

400

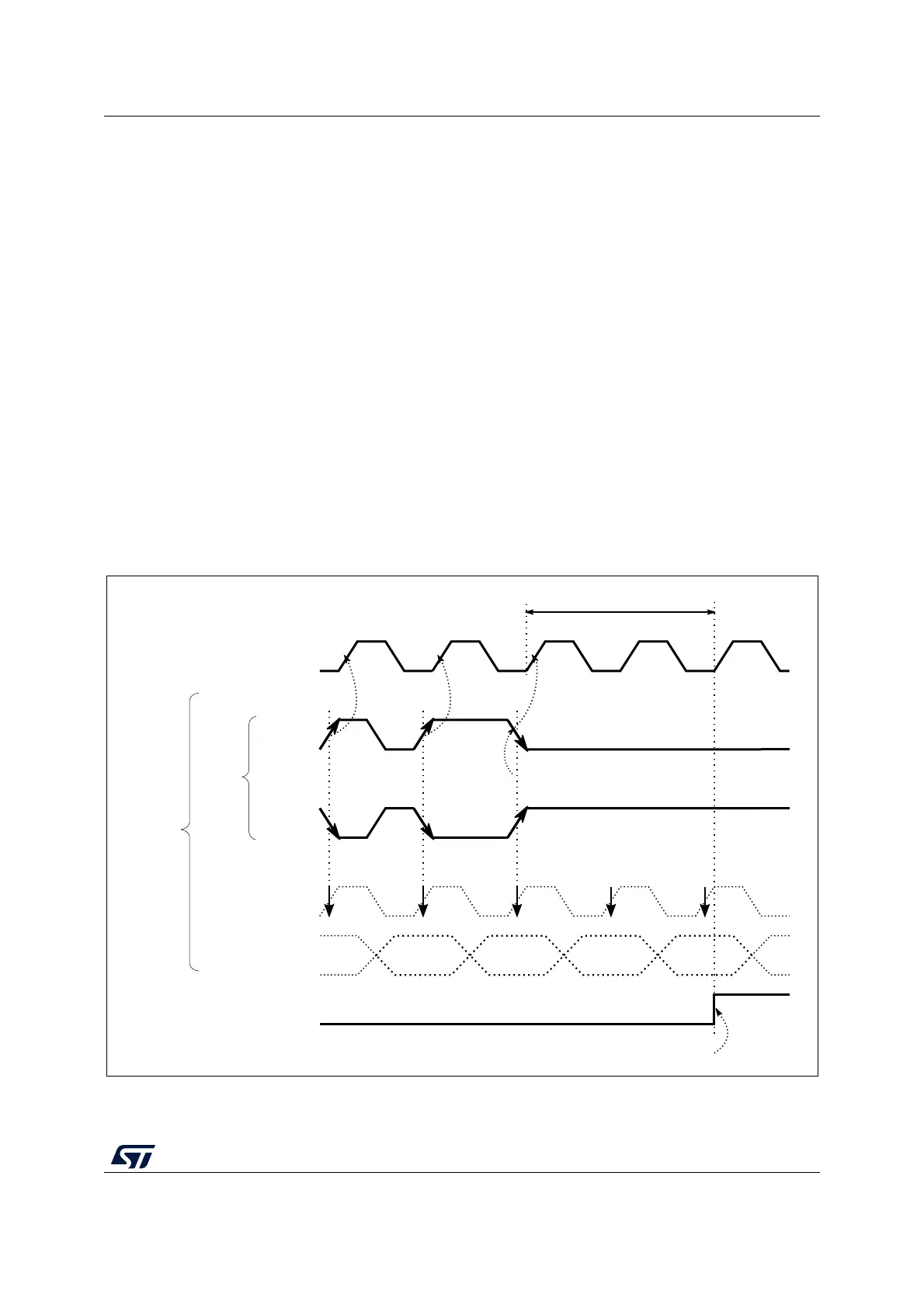

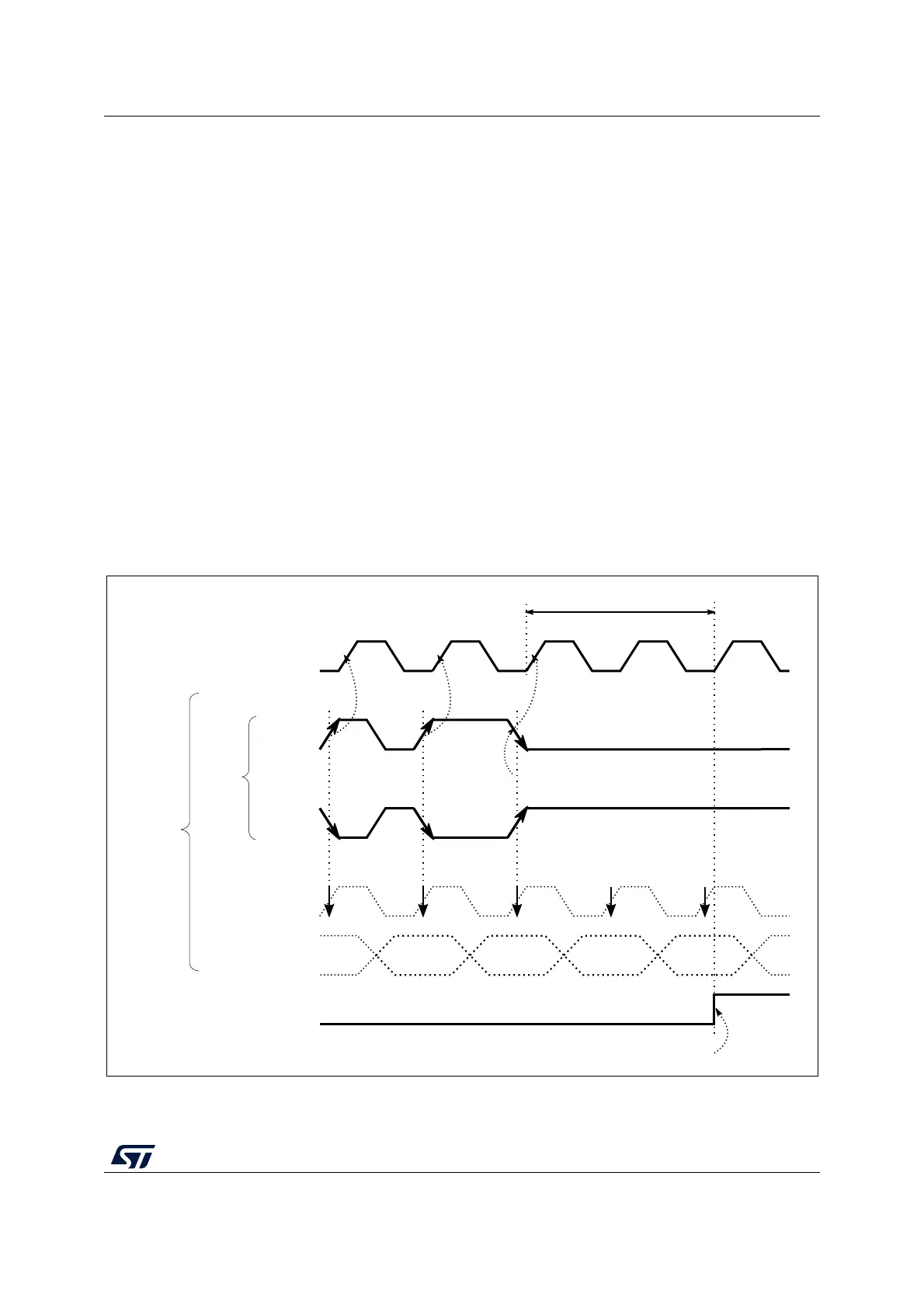

The detection of a clock absence in Manchester coding (after a first successful

synchronization) is based on changes comparison of coded serial data input signal with

output clock generation (CKOUT signal). There must be a voltage level change on DATINy

pin during 2 periods of CKOUT signal (which is controlled by CKOUTDIV bits in

DFSDM_CH0CFGR1 register). This condition also defines the minimum data rate to be able

to correctly recover the Manchester coded data and clock signals.

The maximum data rate of Manchester coded data must be less than the CKOUT signal.

So to correctly receive Manchester coded data, the CKOUTDIV divider must be set

according the formula:

A clock absence flag is set (CKABF[y] = 1) and an interrupt can be invoked (if CKABIE=1) in

case of an input clock recovery error (see CKABF[3:0] in DFSDM_FLT0ISR register and

CKABEN in DFSDM_CHyCFGR1). After a clock absence flag clearing (by CLRCKABF in

DFSDM_FLT0ICR register), the clock absence flag is refreshed.

Figure 71. Clock absence timing diagram for Manchester coding

CKOUTDIV 1+()T

SYSCLK

×()T

Manchester clock

2 CKOUTDIV× T

SYSCLK

×()<<

MS30768V2

CKOUT

recovered clock

SITP = 2

DATINy

SITP = 3

Manchester clock presence

timing

recovered data

1??00

01

last data change

CKABF[y]

error reported

restart counting

max. 2 periods

000

Loading...

Loading...