RM0402 Rev 6 271/1163

RM0402 Flexible static memory controller (FSMC)

287

1. The memory asserts the WAIT signal aligned to NOE/NWE which toggles:

2. The memory asserts the WAIT signal aligned to NEx (or NOE/NWE not toggling):

if

then:

otherwise

where max_wait_assertion_time is the maximum time taken by the memory to assert

the WAIT signal once NEx/NOE/NWE is low.

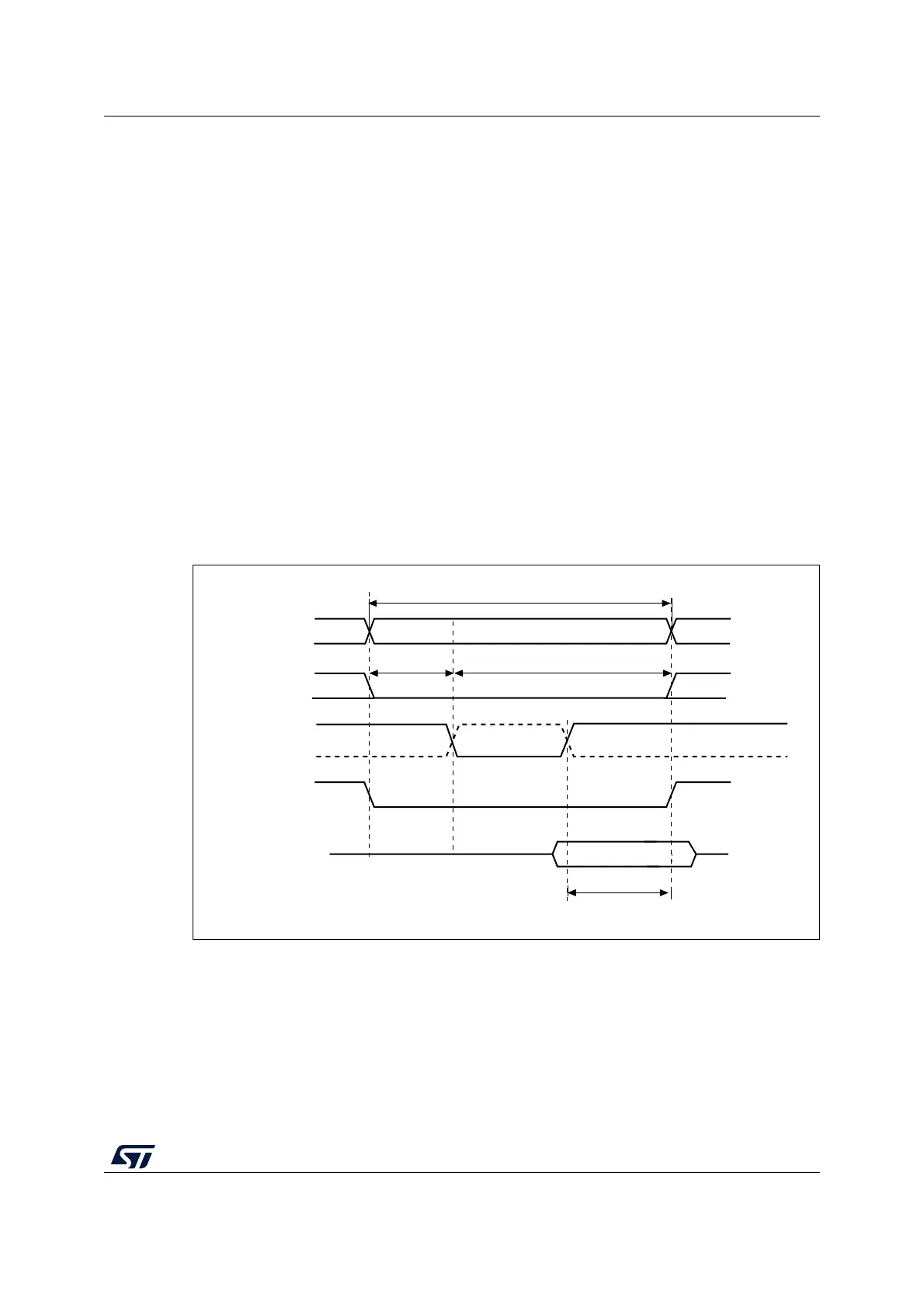

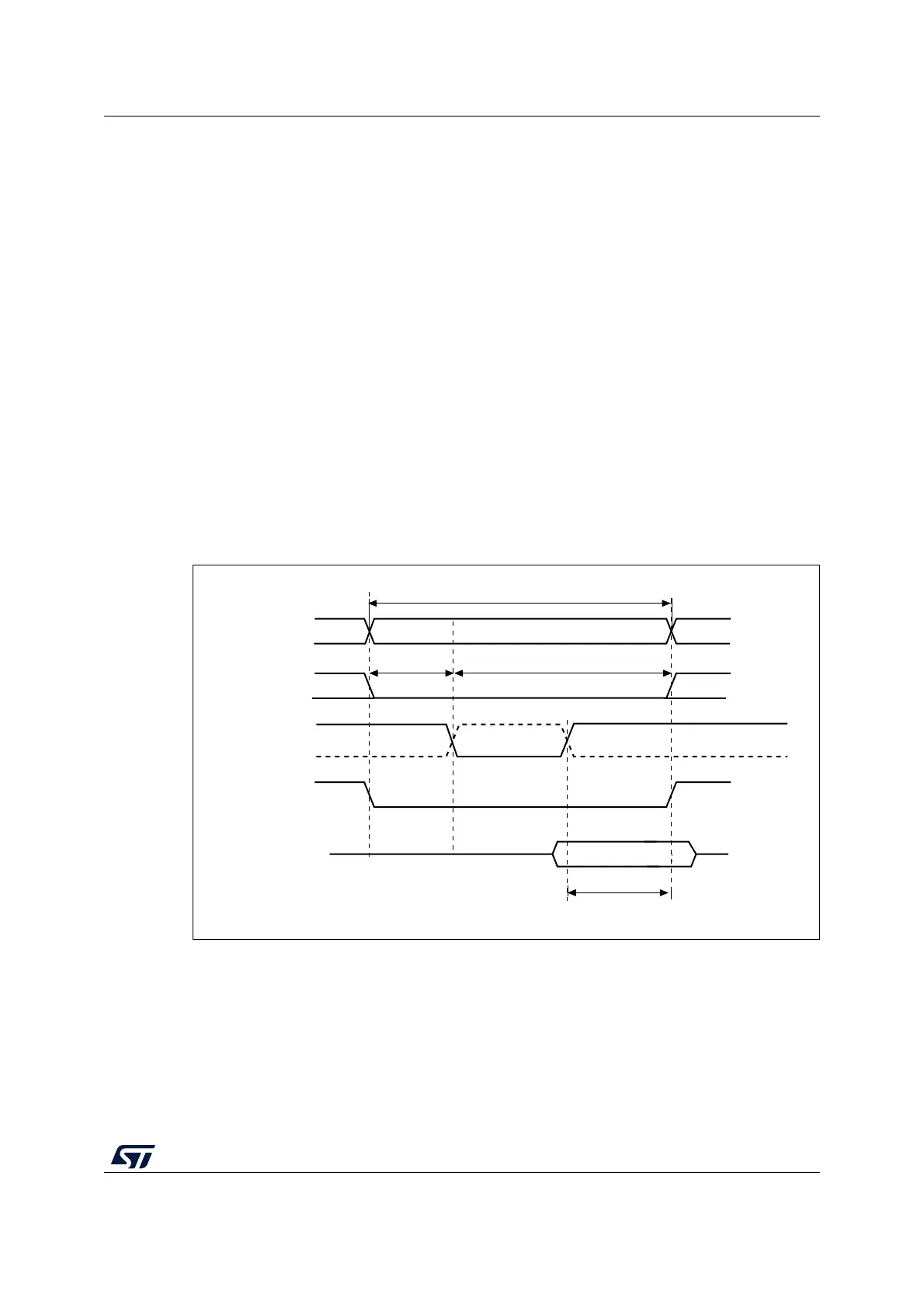

Figure 46 and Figure 47 show the number of HCLK clock cycles that are added to the

memory access phase after WAIT is released by the asynchronous memory (independently

of the above cases).

Figure 46. Asynchronous wait during a read access waveforms

1. NWAIT polarity depends on WAITPOL bit setting in FSMC_BCRx register.

DATAST 4 HCLK×()max_wait_assertion_time+≥

max_wait_assertion_time address_phase hold_phase+>

DATAST 4 HCLK×()max_wait_assertion_time address_phase– hold_phase–()+≥

A[25:0]

NOE

4HCLK

Memory transaction

D[15:0]

NEx

data driven by memory

MS30463V2

address phase

data setup phase

NWAIT

don’t care don’t care

Loading...

Loading...