Advanced-control timers (TIM1&TIM8) RM0402

428/1163 RM0402 Rev 6

16.3.4 Clock selection

The counter clock can be provided by the following clock sources:

• Internal clock (CK_INT)

• External clock mode1: external input pin

• External clock mode2: external trigger input ETR

• Internal trigger inputs (ITRx): using one timer as prescaler for another timer, for

example, Timer 1 can be configured to act as a prescaler for Timer 2. Refer to Using

one timer as prescaler for another timer for more details.

Internal clock source (CK_INT)

If the slave mode controller is disabled (SMS=000), then the CEN, DIR (in the TIMx_CR1

register) and UG bits (in the TIMx_EGR register) are actual control bits and can be changed

only by software (except UG which remains cleared automatically). As soon as the CEN bit

is written to 1, the prescaler is clocked by the internal clock CK_INT.

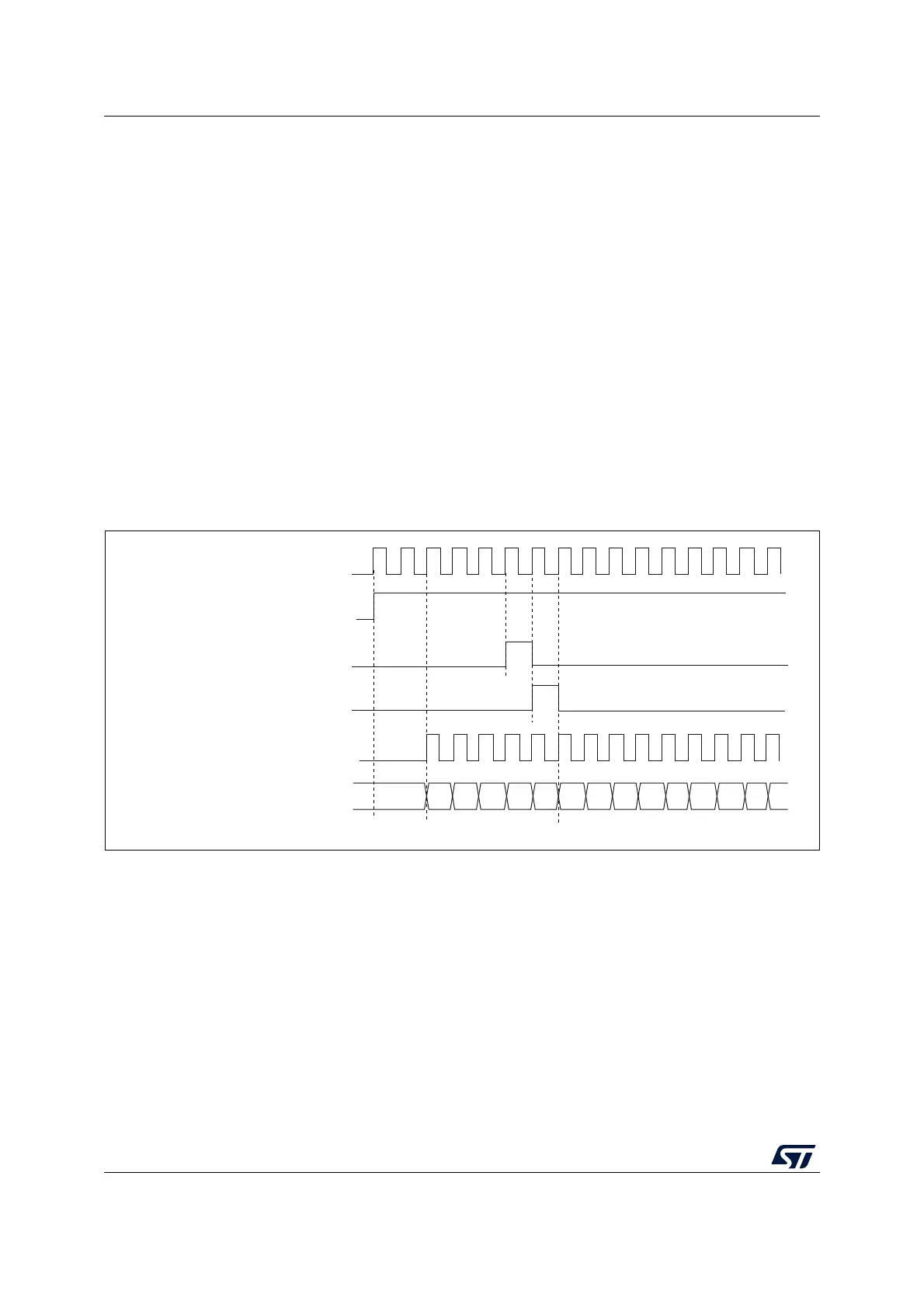

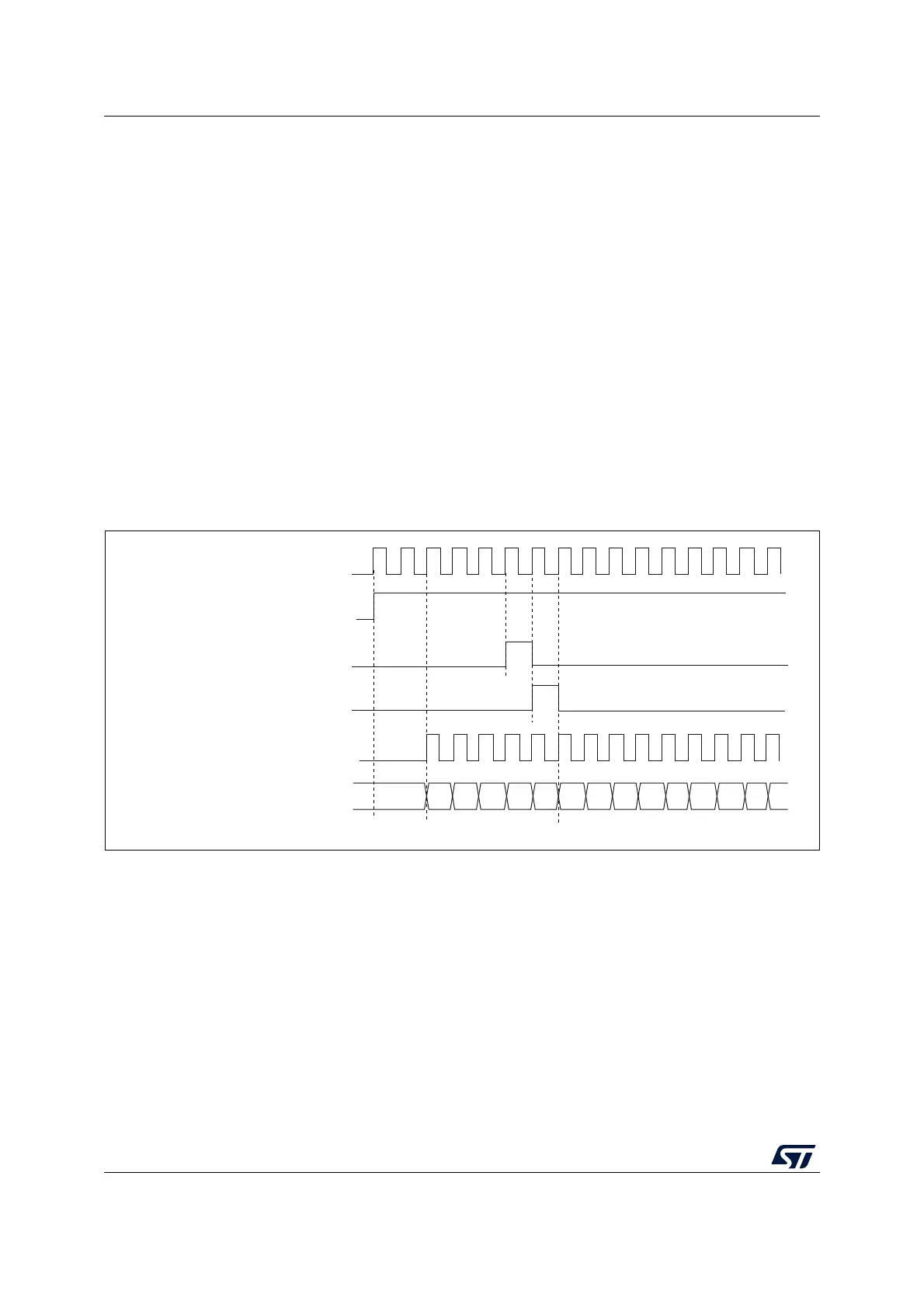

Figure 98 shows the behavior of the control circuit and the upcounter in normal mode,

without prescaler.

Figure 98. Control circuit in normal mode, internal clock divided by 1

External clock source mode 1

This mode is selected when SMS=111 in the TIMx_SMCR register. The counter can count at

each rising or falling edge on a selected input.

Internal clock

Counter clock = CK_CNT = CK_PSC

Counter register

CEN=CNT_EN

UG

CNT_INIT

MS31085V2

00

02

03

04 05

06 0732

33

34 35 36

31

01

Loading...

Loading...