RM0402 Rev 6 249/1163

RM0402 Flexible static memory controller (FSMC)

287

transactions are allowed (the controller reads the entire 16-bit memory word and

uses only the required byte).

Wrap support for NOR Flash/PSRAM

Wrap burst mode for synchronous memories is not supported. The memories must be

configured in Linear burst mode of undefined length.

Configuration registers

The FSMC can be configured through a set of registers. Refer to Section 11.6.6, for a

detailed description of the NOR Flash/PSRAM controller registers.

11.5 External device address mapping

From the FSMC point of view, the external memory is divided into fixed-size banks of

256

Mbytes each (see Figure 32):

• Bank 1 used to address up to 4 NOR Flash memory or PSRAM devices. This bank is

split into 4 NOR/PSRAM subbanks with 4 dedicated chip selects, as follows:

– Bank 1 - NOR/PSRAM 1

– Bank 1 - NOR/PSRAM 2

– Bank 1 - NOR/PSRAM 3

– Bank 1 - NOR/PSRAM 4

• Bank 3 used to address NAND Flash memory devices.The MPU memory attribute for

this space must be reconfigured by software to Device.

For each bank the type of memory to be used can be configured by the user application

through the Configuration register.

Figure 32. FSMC memory banks

11.5.1 NOR/PSRAM address mapping

HADDR[27:26] bits are used to select one of the four memory banks as shown in Table 42.

MS34476V1

Supported memory type

Bank 1

4 x 64 MB

NOR/PSRAM/SRAM

Bank

0x6000 0000

Address

0x6FFF FFFF

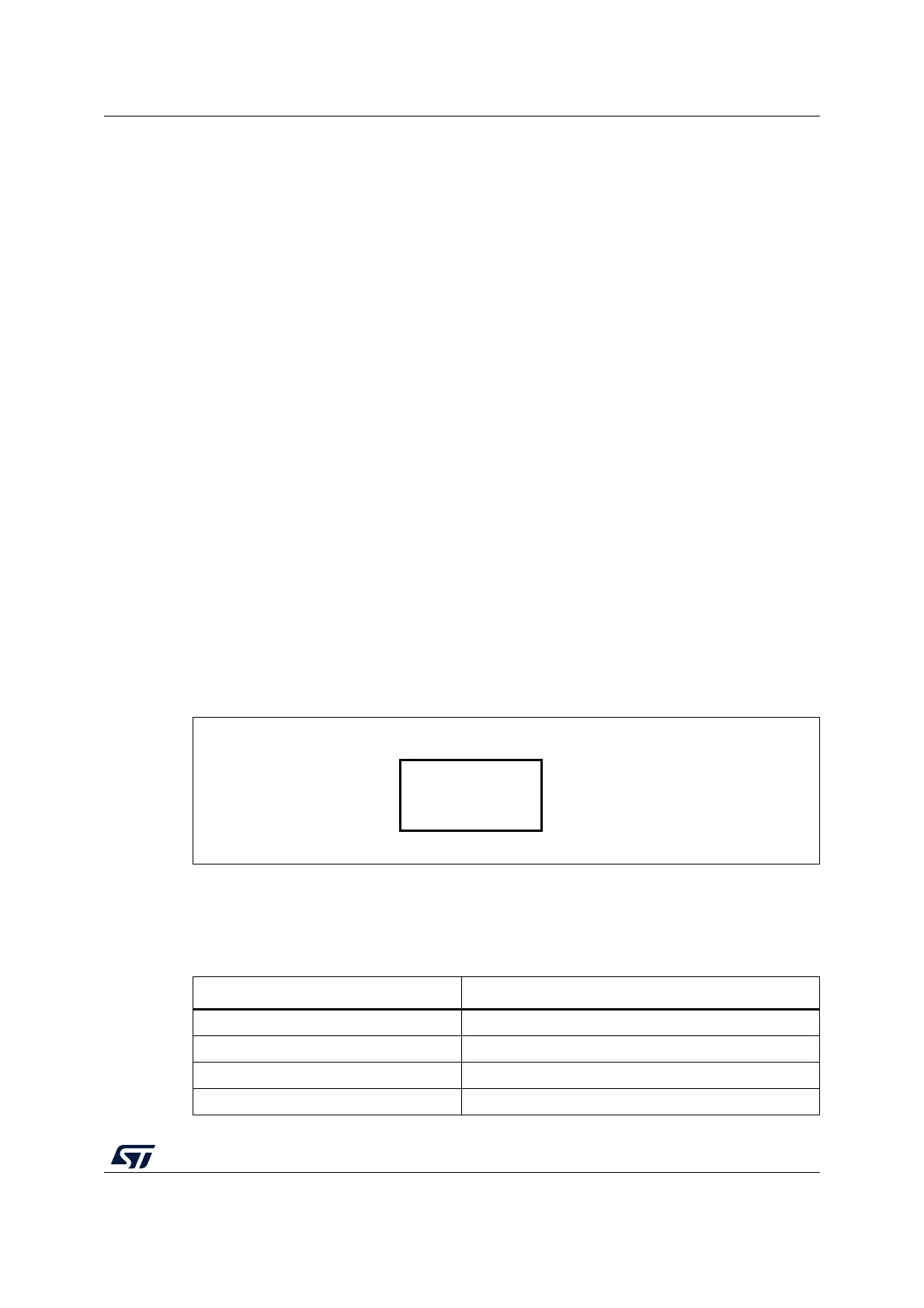

Table 42. NOR/PSRAM bank selection

HADDR[27:26]

(1)

Selected bank

00 Bank 1 - NOR/PSRAM 1

01 Bank 1 - NOR/PSRAM 2

10 Bank 1 - NOR/PSRAM 3

11 Bank 1 - NOR/PSRAM 4

Loading...

Loading...