Flexible static memory controller (FSMC) RM0402

286/1163 RM0402 Rev 6

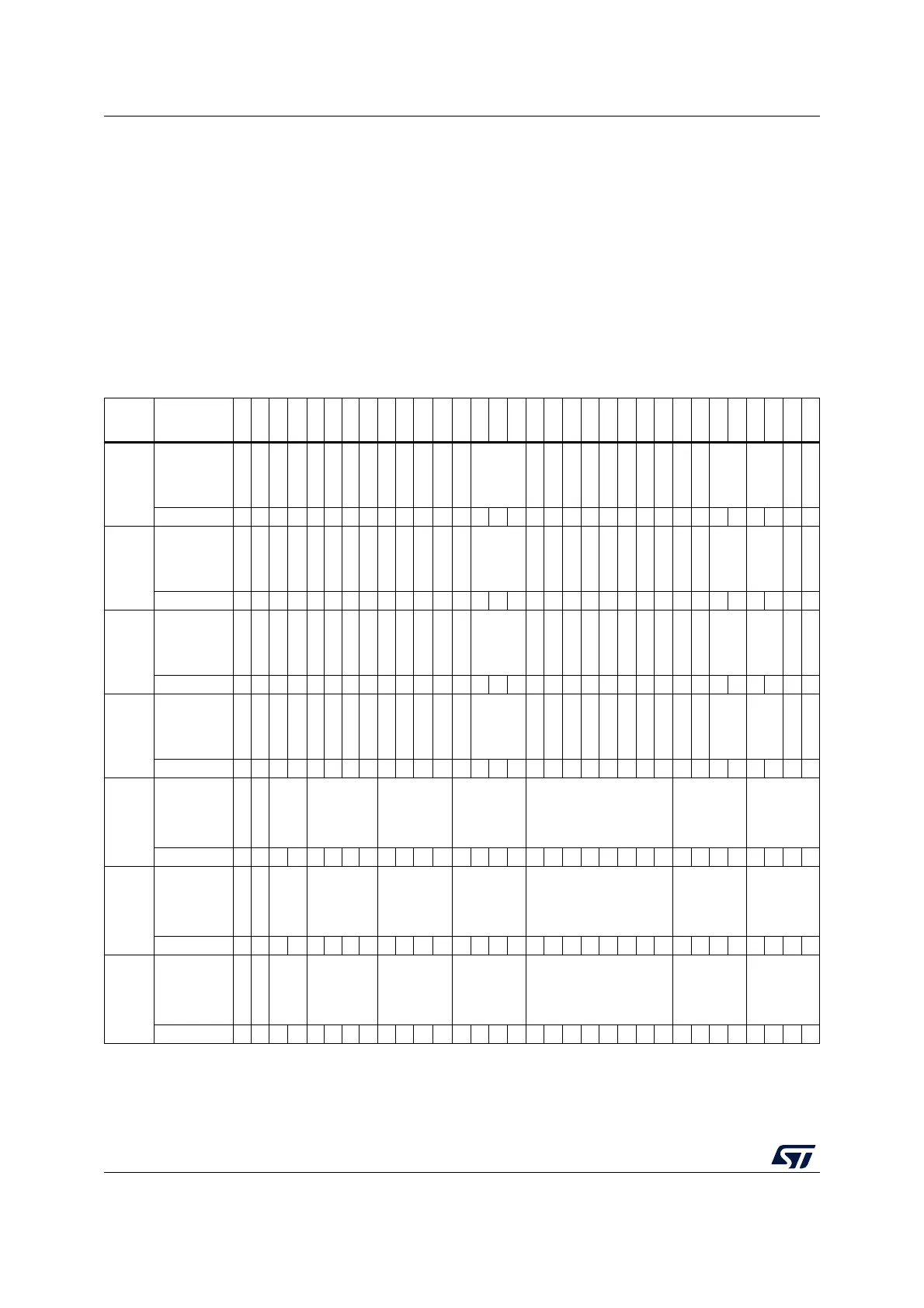

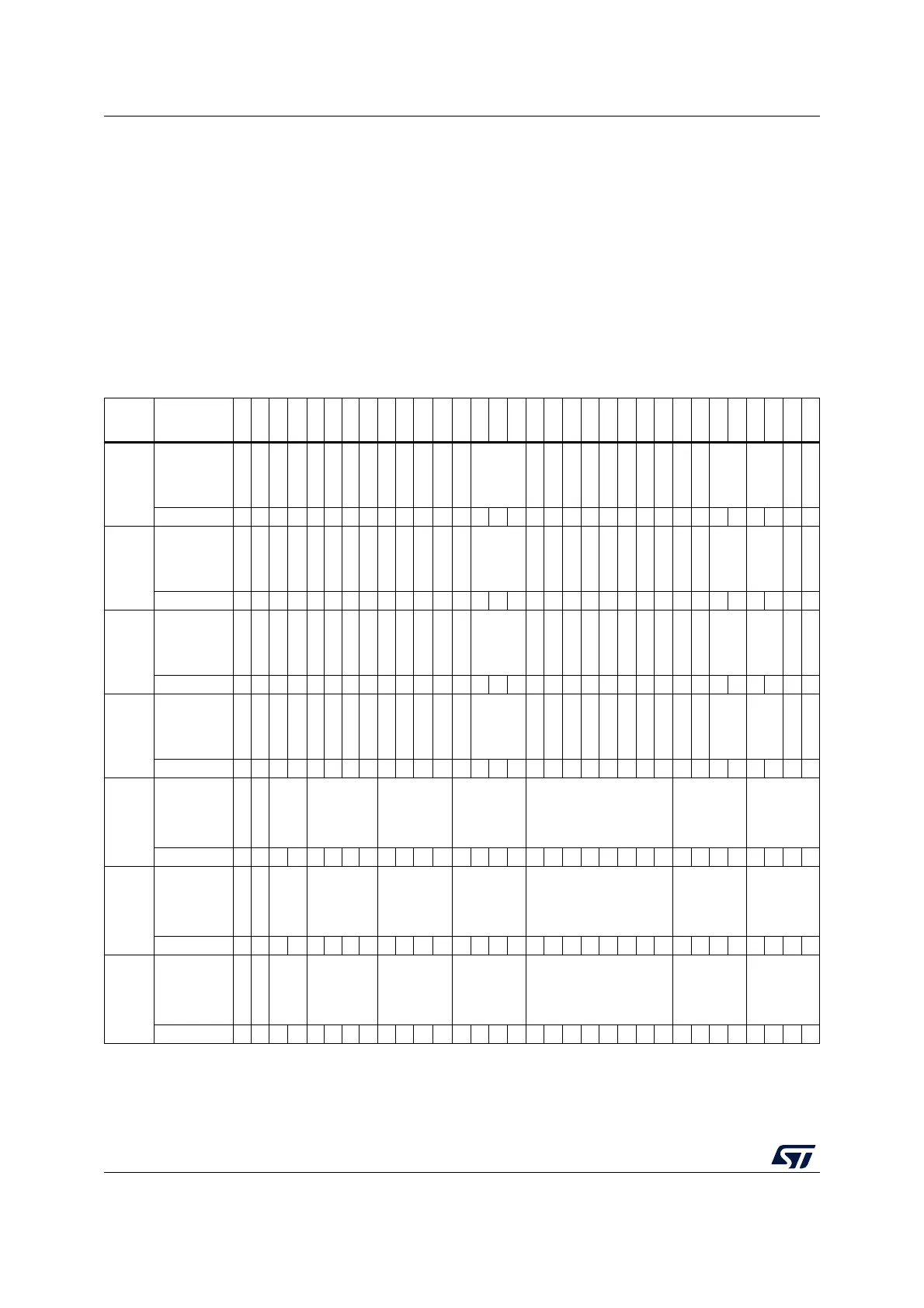

11.6.7 FSMC register map

Bits 3:0 ADDSET[3:0]: Address setup phase duration.

These bits are written by software to define the duration of the address setup phase in HCLK cycles

(refer to Figure 33 to Figure 45), used in asynchronous accesses:

0000: ADDSET phase duration = 0 × HCLK clock cycle

...

1111: ADDSET phase duration = 15 × HCLK clock cycles (default value after reset)

Note: In synchronous accesses, this value is not used, the address setup phase is always 1 Flash

clock period duration. In muxed mode, the minimum ADDSET value is 1.

Table 70. FSMC register map and reset values

Offset Register

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

0x00

FSMC_BCR1

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

WFDIS

CCLKEN

CBURSTRW

CPSIZE

[2:0]

ASYNCWAIT

EXTMOD

WAITEN

WREN

WAITCFG

Res.

WAITPOL

BURSTEN

Res.

FACCEN

MWID

[1:0]

MTYP

[1:0]

MUXEN

MBKEN

Reset value 0 0000000110 00 1011011

0x08

FSMC_BCR2

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

CBURSTRW

CPSIZE

[2:0]

ASYNCWAIT

EXTMOD

WAITEN

WREN

WAITCFG

Res.

WAITPOL

BURSTEN

Res.

FACCEN

MWID

[1:0]

MTYP

[1:0]

MUXEN

MBKEN

Reset value 000000110 00 1010010

0x10

FSMC_BCR3

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

CBURSTRW

CPSIZE

[2:0]

ASYNCWAIT

EXTMOD

WAITEN

WREN

WAITCFG

Res.

WAITPOL

BURSTEN

Res.

FACCEN

MWID

[1:0]

MTYP

[1:0]

MUXEN

MBKEN

Reset value 000000110 00 1010010

0x18

FSMC_BCR4

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

CBURSTRW

CPSIZE

[2:0]

ASYNCWAIT

EXTMOD

WAITEN

WREN

WAITCFG

Res.

WAITPOL

BURSTEN

Res.

FACCEN

MWID

[1:0]

MTYP

[1:0]

MUXEN

MBKEN

Reset value 000000110 00 1010010

0x04

FSMC_BTR1

Res.

Res.

ACCMOD[1:0]

DATLAT[3:0] CLKDIV[3:0]

BUSTURN[3:0

]

DATAST[7:0] ADDHLD[3:0] ADDSET[3:0]

Reset value 001111111 111111111111111111111

0x0C

FSMC_BTR2

Res.

Res.

ACCMOD[1:0]

DATLAT[3:0] CLKDIV[3:0]

BUSTURN[3:0

]

DATAST[7:0] ADDHLD[3:0] ADDSET[3:0]

Reset value 001111111 111111111111111111111

0x14

FSMC_BTR3

Res.

Res.

ACCMOD[1:0]

DATLAT[3:0] CLKDIV[3:0]

BUSTURN[3:0

]

DATAST[7:0] ADDHLD[3:0] ADDSET[3:0]

Reset value 001111111 111111111111111111111

Loading...

Loading...