RM0402 Rev 6 425/1163

RM0402 Advanced-control timers (TIM1&TIM8)

483

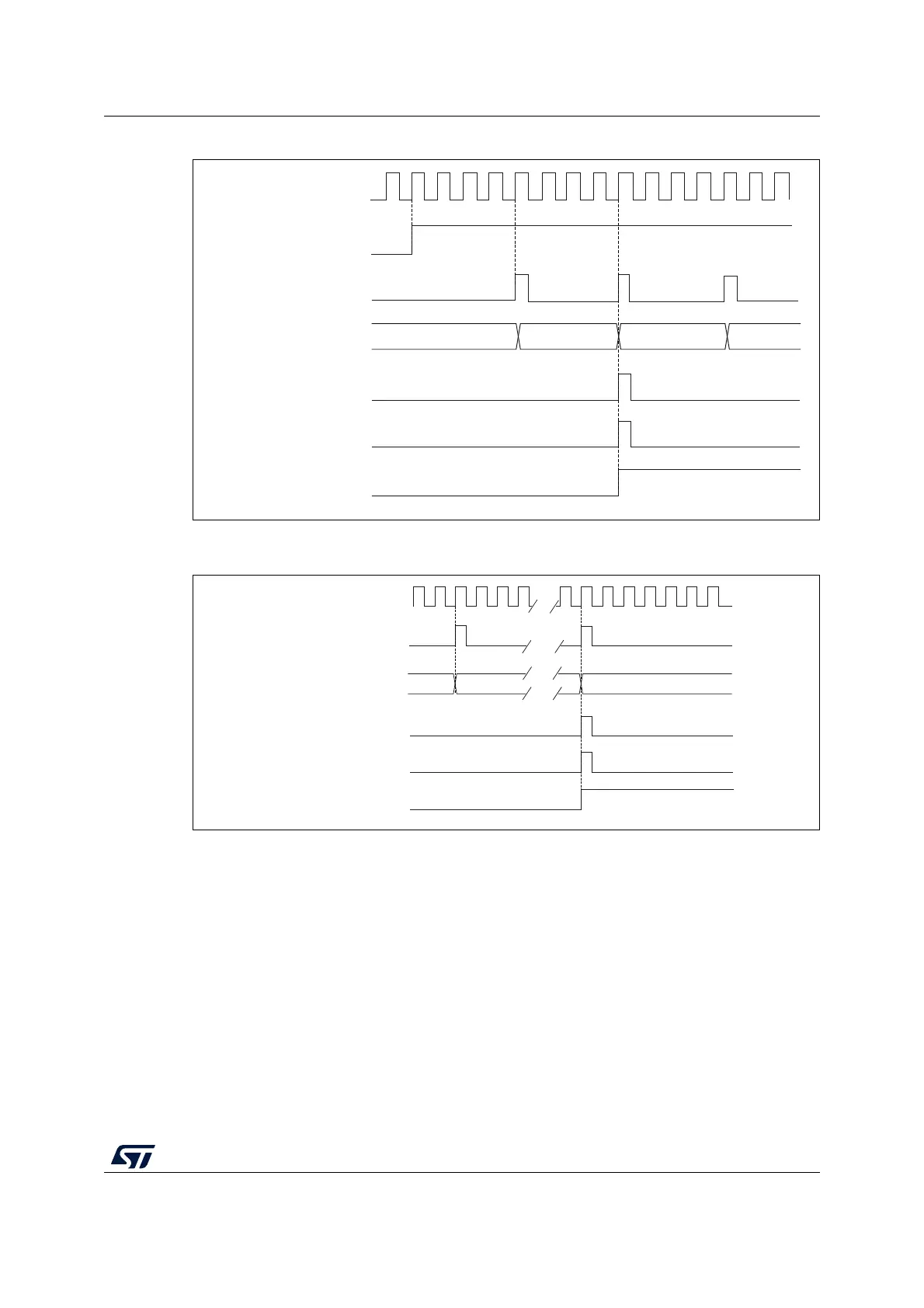

Figure 93. Counter timing diagram, internal clock divided by 4, TIMx_ARR=0x36

1. Center-aligned mode 2 or 3 is used with an UIF on overflow.

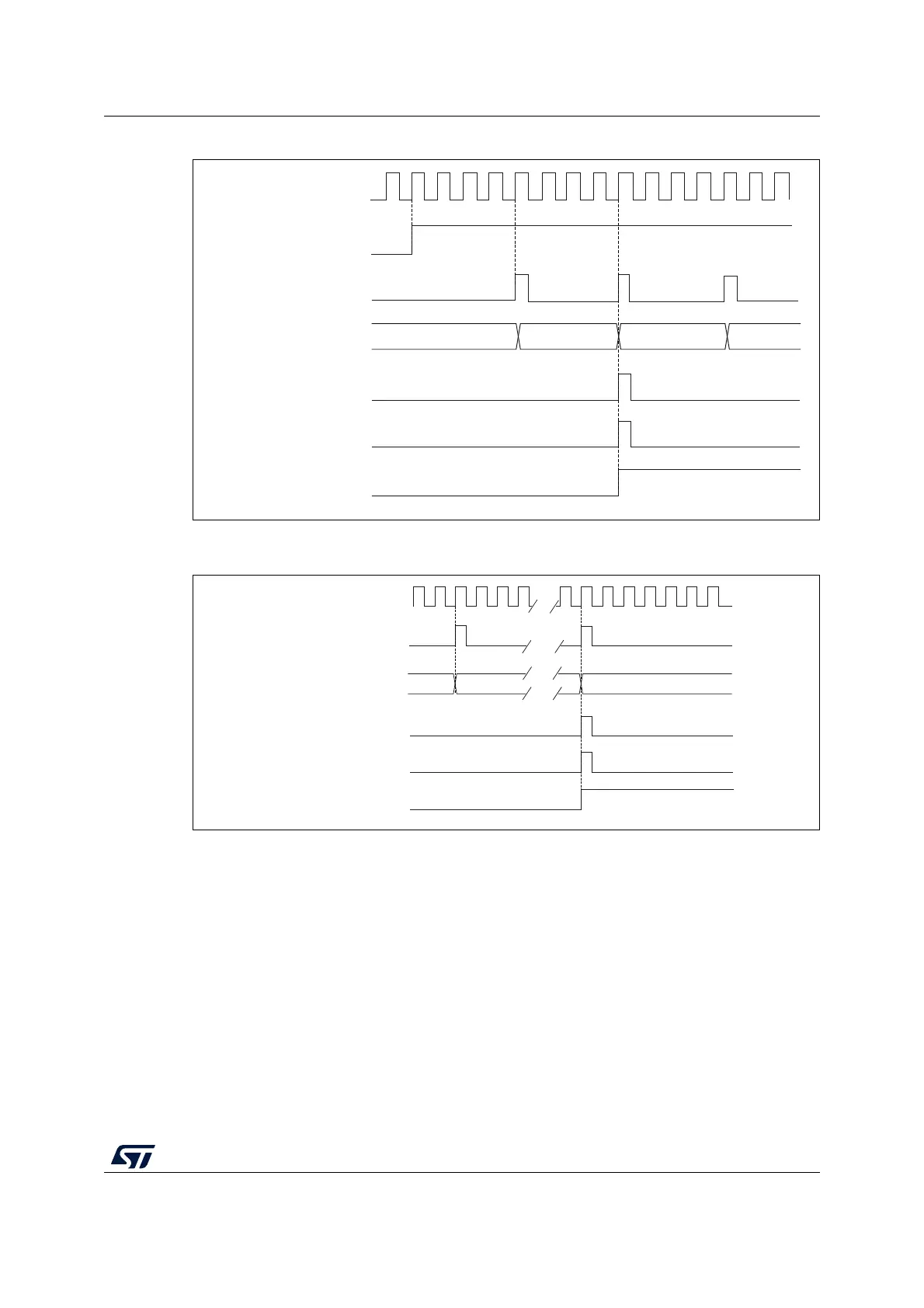

Figure 94. Counter timing diagram, internal clock divided by N

0034 0035

MS31191V2

CK_PSC

Timerclock = CK_CNT

Counter register

Update event (UEV)

Counter overflow

Update interrupt flag (UIF)

CNT_EN

0036 0035

MS31192V2

CK_PSC

Timerclock = CK_CNT

Counter register

Update event (UEV)

Update interrupt flag (UIF)

Counter underflow

001F20 01

Loading...

Loading...