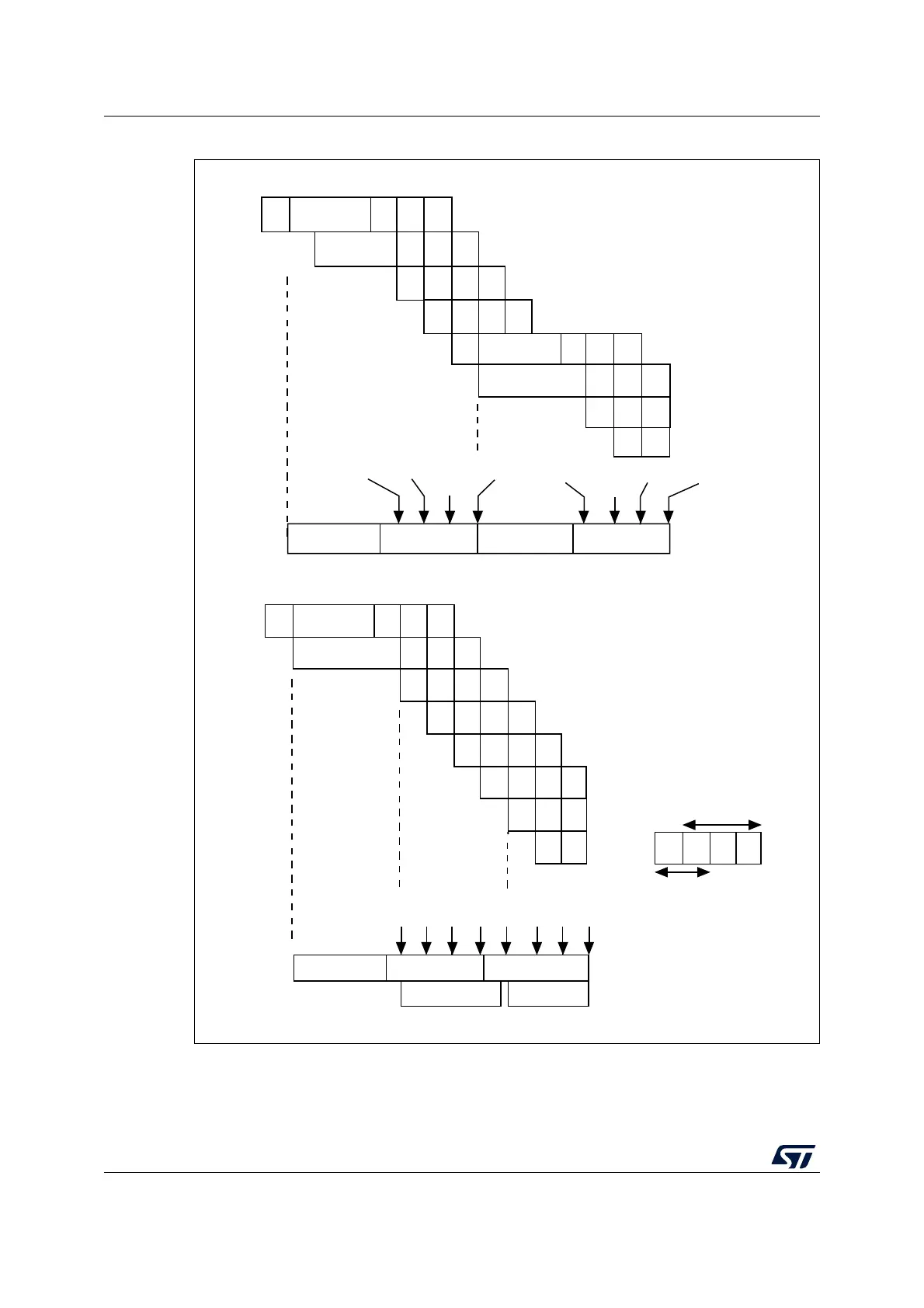

Figure 4. Sequential 32-bit instruction execution

@

@

@

@

F

F

F

F

D

D

D

D

E

E

E

E

@

@

@

@

F

F

F

F

D

D

D

E

E

1111

2222

3333

444 4

5555

6666

777

88

Read ins 1, 2, 3, 4 Gives ins 1, 2, 3, 4 Read ins 5, 6, 7, 8 Gives ins 5, 6, 7, 8

ins 1

fetch

ins 2

fetch

ins 3

fetch

ins 4

fetch

ins 5

fetch

ins 6

fetch

ins 7

fetch

ins 8

fetch

WAIT

WAIT

DE

44

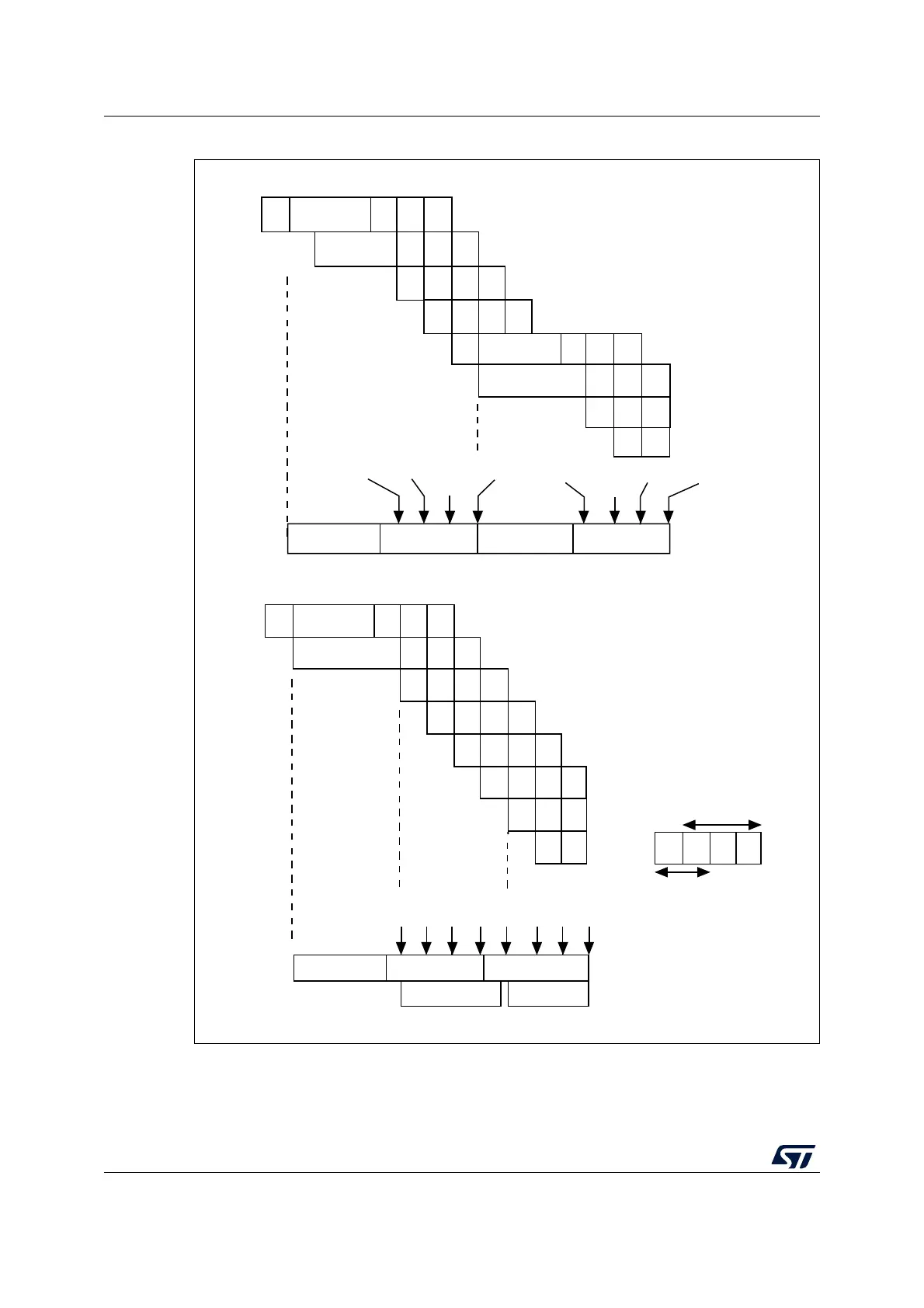

@

@

F

F

F

F

D

D

D

E

E

5

55

66 6

777

88

@

@

@

@

@

F

F

F

F

D

D

D

E

E

Wait data

@

1111

2222

333

44

5

E

3

Read ins 1, 2, 3, 4 Gives ins 1, 2, 3, 4 Gives ins 5, 6, 7, 8

Read ins 5, 6, 7, 8 Read ins 9, 10, ...

ins 4 ins 5

fetch

ins 6 ins 7

Without prefetch

With prefetch

FDE

@

Cortex-M4 pipeline

AHB protocol

@ : address requested

F: Fetch stage

D: Decode stage

E: Execute stage

ins 1

fetch

ins 2

fetch

ins 3

fetch fetch fetch fetch

ins 8

fetch

MS31831V1

Loading...

Loading...