Flexible static memory controller (FSMC) RM0402

254/1163 RM0402 Rev 6

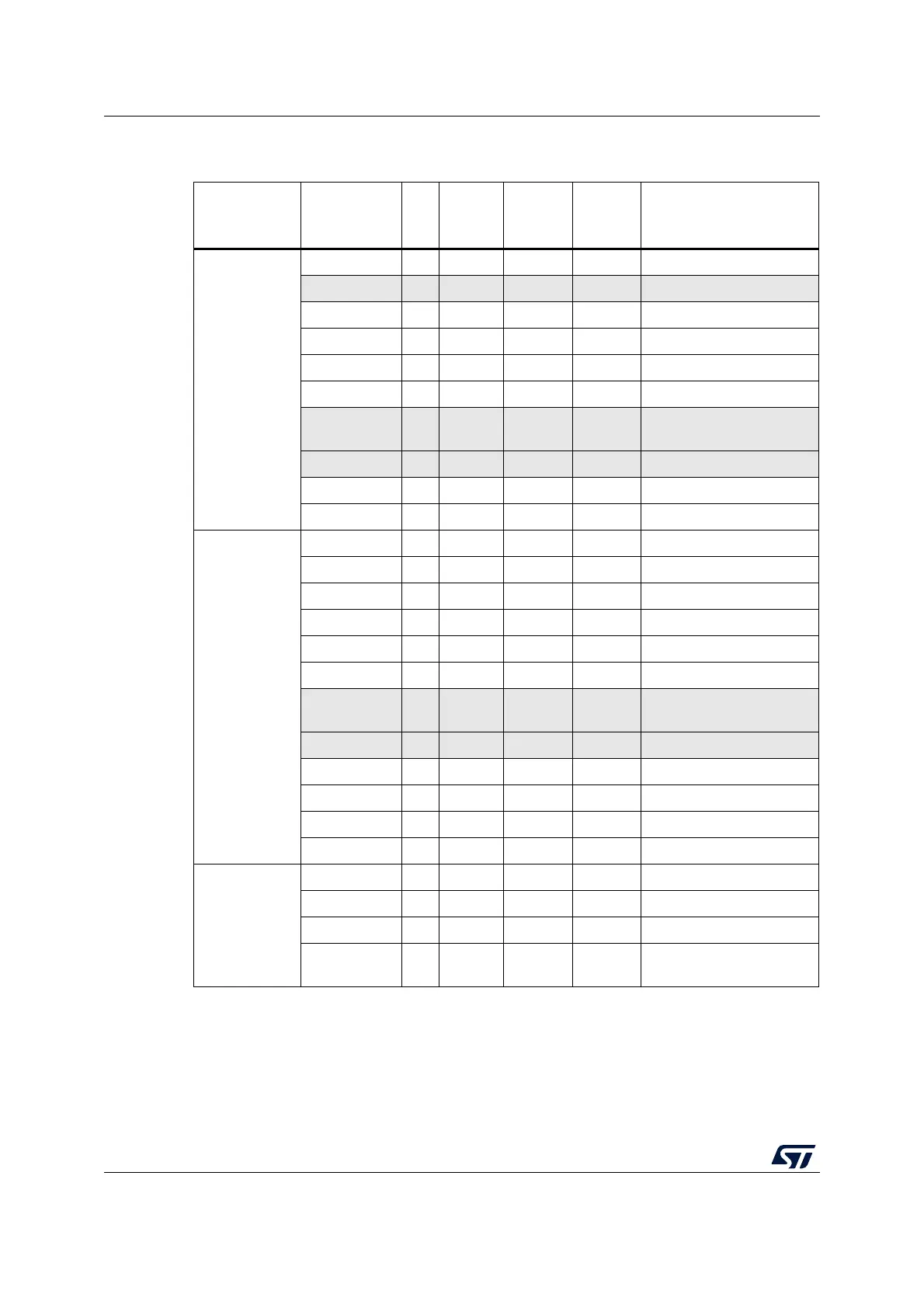

Table 49. NOR Flash/PSRAM: example of supported memories

and transactions

Device Mode R/W

AHB

data

size

Memory

data size

Allowed/

not

allowed

Comments

NOR Flash

(muxed I/Os

and nonmuxed

I/Os)

Asynchronous R 8 16 Y -

Asynchronous W 8 16 N -

Asynchronous R 16 16 Y -

Asynchronous W 16 16 Y -

Asynchronous R 32 16 Y Split into 2 FSMC accesses

Asynchronous W 32 16 Y Split into 2 FSMC accesses

Asynchronous

page

R - 16 N Mode is not supported

Synchronous R 8 16 N -

Synchronous R 16 16 Y -

Synchronous R 32 16 Y -

PSRAM

(multiplexed

I/Os and non-

multiplexed

I/Os)

Asynchronous R 8 16 Y -

Asynchronous W 8 16 Y Use of byte lanes NBL[1:0]

Asynchronous R 16 16 Y -

Asynchronous W 16 16 Y -

Asynchronous R 32 16 Y Split into 2 FSMC accesses

Asynchronous W 32 16 Y Split into 2 FSMC accesses

Asynchronous

page

R - 16 N Mode is not supported

Synchronous R 8 16 N -

Synchronous R 16 16 Y -

Synchronous R 32 16 Y -

Synchronous W 8 16 Y Use of byte lanes NBL[1:0]

Synchronous W 16/32 16 Y -

SRAM and

ROM

Asynchronous R 8 / 16 16 Y -

Asynchronous W 8 / 16 16 Y Use of byte lanes NBL[1:0]

Asynchronous R 32 16 Y Split into 2 FSMC accesses

Asynchronous W 32 16 Y

Split into 2 FSMC accesses

Use of byte lanes NBL[1:0]

Loading...

Loading...