RM0402 Rev 6 159/1163

RM0402 Reset and clock control (RCC) for STM32F412xx

166

6.3.23 RCC PLLI2S configuration register (RCC_PLLI2SCFGR)

Address offset: 0x84

Reset value: 0x2400 3010

Access: no wait state, word, half-word and byte access.

This register is used to configure the PLLI2S clock outputs according to the formulas:

• f

(VCO clock)

= f

(PLLI2S clock input)

× (PLLI2SN / PLLI2SM)

• f(

USB OTG FS, SDIO, RNG clock output

) = f(

VCO clock

) / PLLQ

• f(

DFSDM, I2S clock output

) = f(

VCO clock

) / PLLR

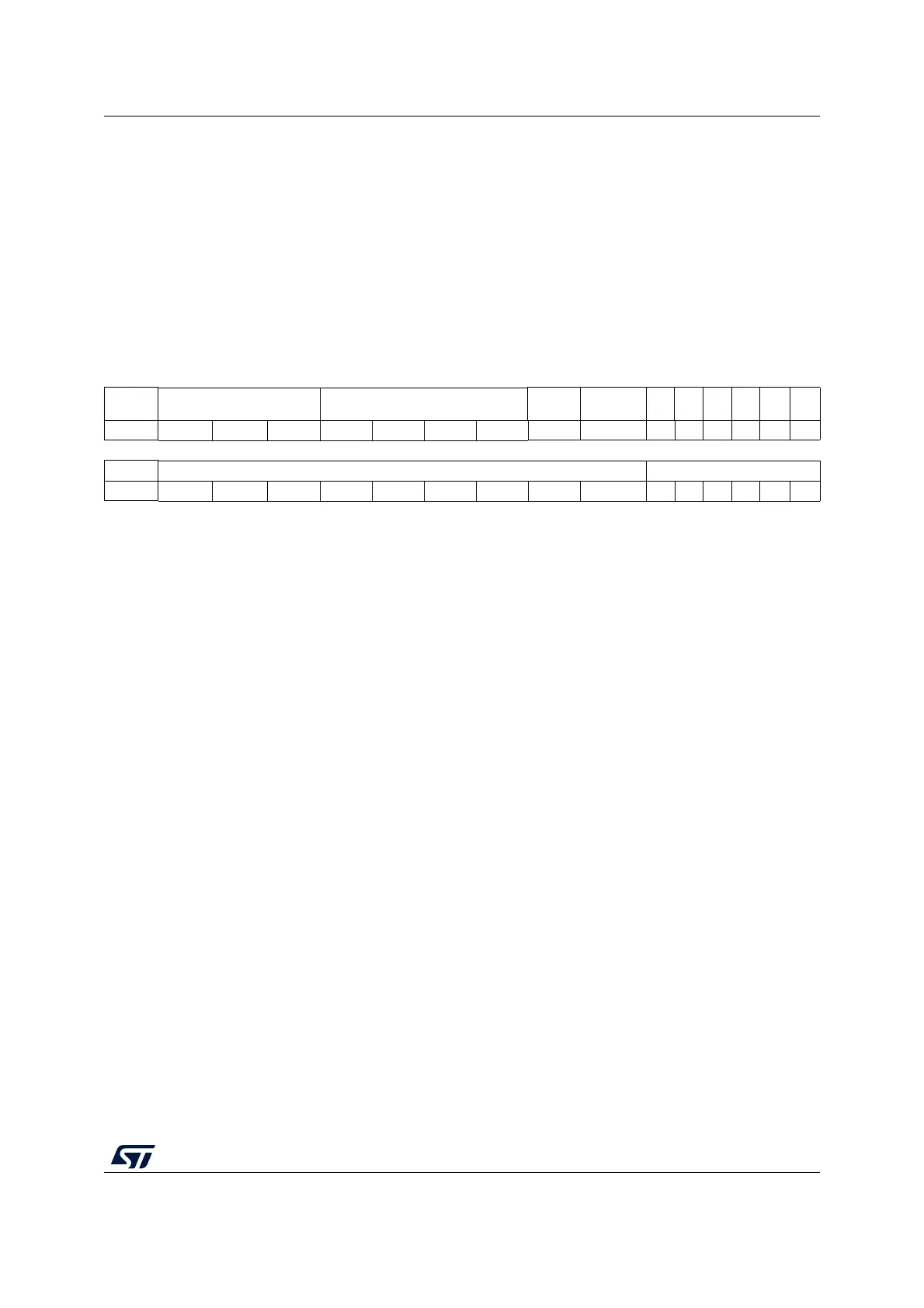

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. PLLI2SR[2:0] PLLI2SQ[3:0] Res. PLLI2SSRC

Res

.

Res

.

Res

.

Res

.

Res. Res.

rw rw rw rw rw rw rw rw

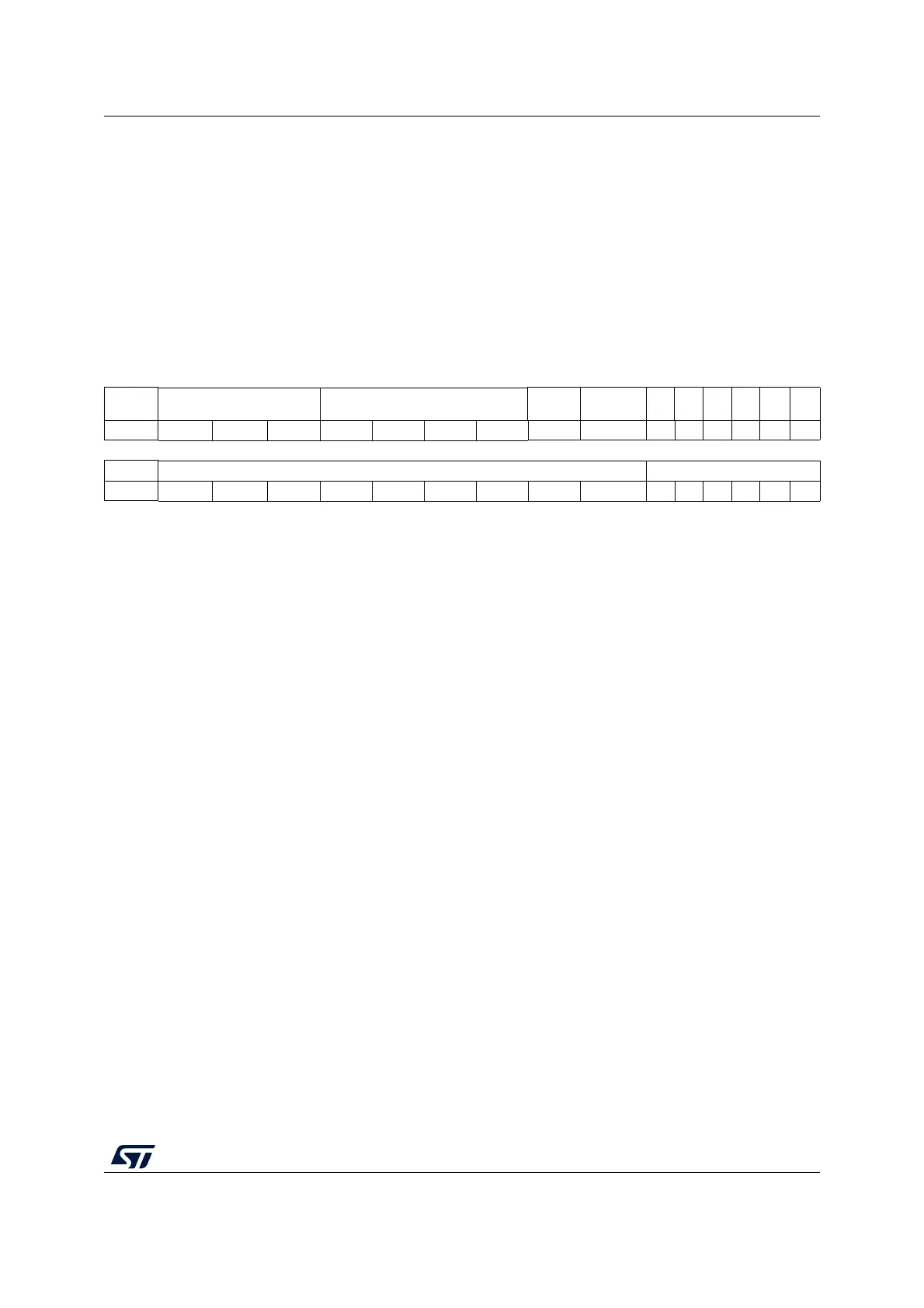

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Res. PLLI2SN[8:0] PLLI2SM[5:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bit 31 Reserved, must be kept at reset value.

Bits 30:28 PLLI2SR[2:0]: PLLI2S division factor for I2S clocks

Set and cleared by software to control the I2S clock frequency. These bits should be written

only if the PLLI2S is disabled. The factor must be chosen in accordance with the prescaler

values inside the I2S peripherals, to reach 0.3% error when using standard crystals and 0%

error with audio crystals. For more information about I2S clock frequency and precision, refer

to

Section 26.6.4: Clock generator in the I2S chapter.

Caution: The I2Ss requires a frequency lower than or equal to 192 MHz to work correctly.

I2S clock frequency = VCO frequency / PLLR with 2 ≤ PLLR ≤ 7

000: PLLR = 0, wrong configuration

001: PLLR = 1, wrong configuration

010: PLLR = 2

...

111: PLLR = 7

Bits 27:24 PLLI2SQ[3:0]: PLLI2S division factor for USB OTG FS/SDIO/RNG clock

Set and cleared by software to control the USB OTG FS/SDIO/RNG clock frequency. These

bits can be written only when the PLLI2S is disabled.

USB OTG FS/SDIO/RNG clock frequency = VCO frequency / PLLI2SQ with 2 ≤ PLLI2SQ ≤

15

0000: PLLI2SQ = 0, wrong configuration

0001: PLLI2SQ = 1, wrong configuration

0010: PLLI2SQ = 2

0011: PLLI2SQ = 3

0100: PLLI2SQ = 4

0101: PLLI2SQ = 5

...

1111: PLLI2SQ = 15

Bit 23 Reserved, must be kept at reset value.

Loading...

Loading...