Serial peripheral interface/ inter-IC sound (SPI/I2S) RM0402

818/1163 RM0402 Rev 6

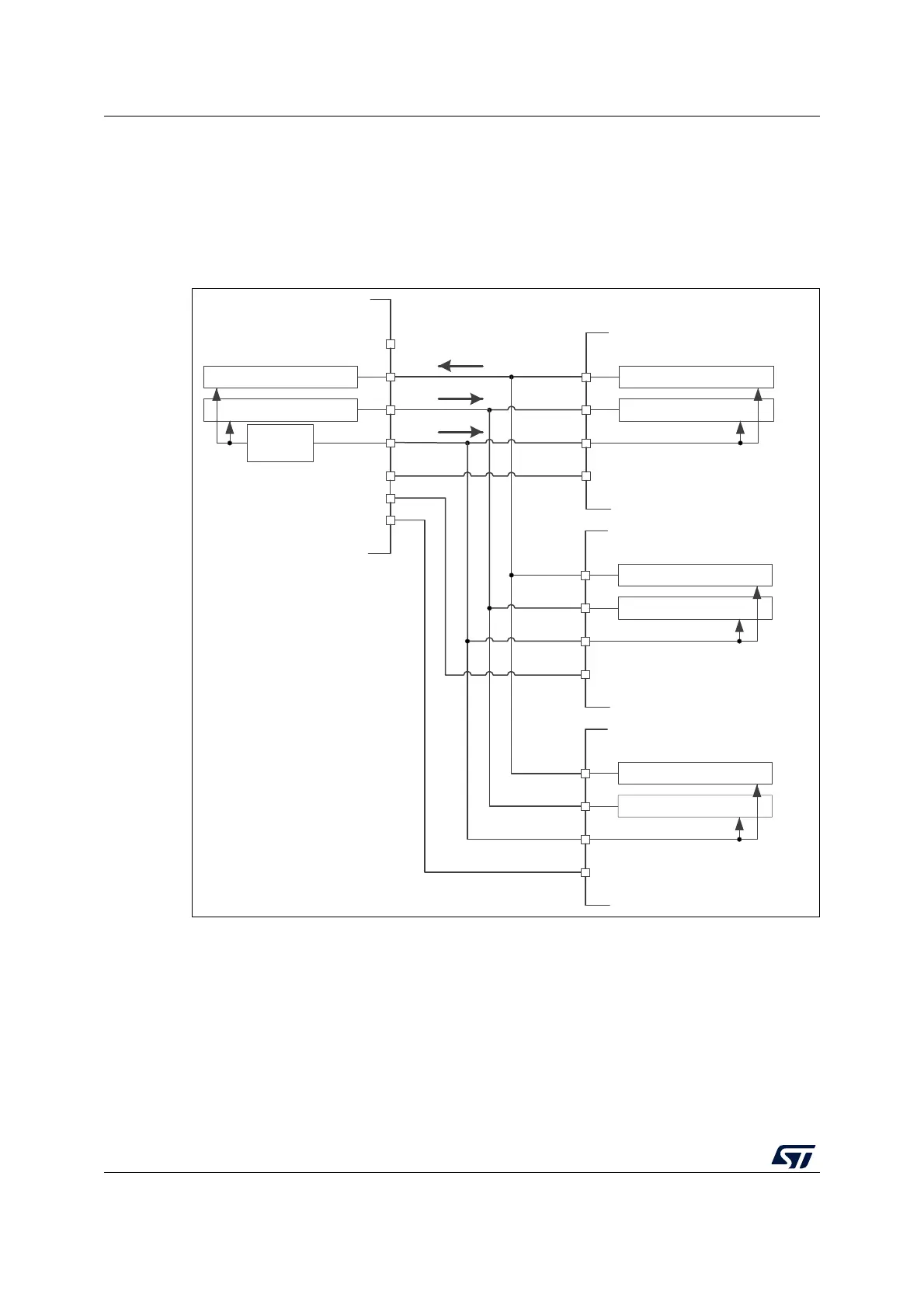

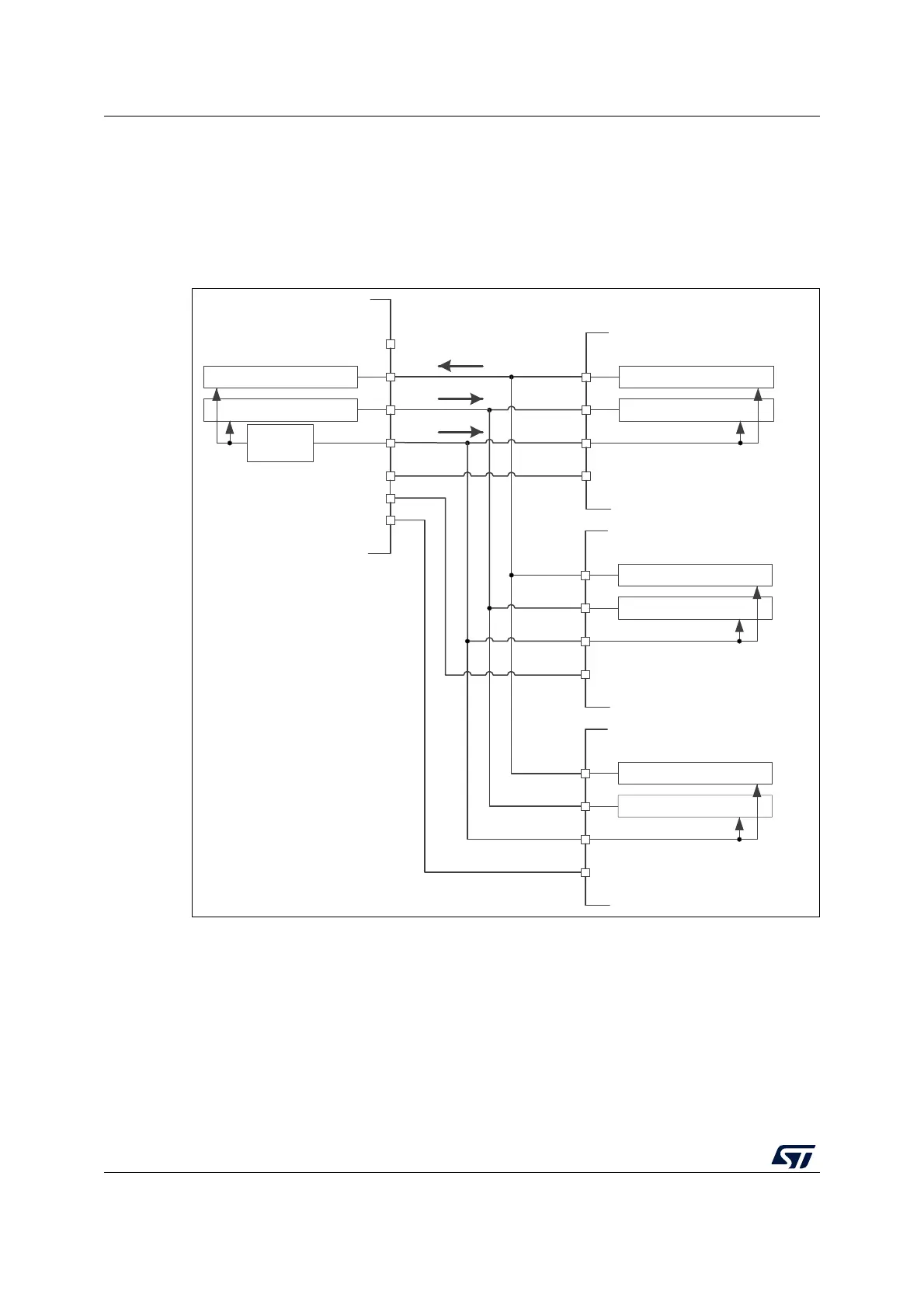

26.3.3 Standard multi-slave communication

In a configuration with two or more independent slaves, the master uses GPIO pins to

manage the chip select lines for each slave (see

Figure 274.). The master must select one

of the slaves individually by pulling low the GPIO connected to the slave NSS input. When

this is done, a standard master and dedicated slave communication is established.

Figure 274. Master and three independent slaves

1. NSS pin is not used on master side at this configuration. It has to be managed internally (SSM=1, SSI=1) to

prevent any MODF error.

2. As MISO pins of the slaves are connected together, all slaves must have the GPIO configuration of their

MISO pin set as alternate function open-drain (see Section 7.3.7: I/O alternate function input/output on

page 174).

Rx shift register

Tx shift register Rx shift register

Tx shift register

SPI clock

generator

Master

Slave 1

MISO

MOSI

SCK

NSS

MISO

MOSI

SCK

NSS

(1)

Rx shift register

Tx shift register

Slave 2

Rx shift register

Tx shift register

Slave 3

IO1

IO2

IO3

MISO

MOSI

SCK

NSS

MISO

MOSI

SCK

NSS

MSv39626V1

Loading...

Loading...