RM0402 Rev 6 391/1163

RM0402 Digital filter for sigma delta modulators (DFSDM)

400

14.8.8 DFSDM filter x data register for the regular channel

(DFSDM_FLTxRDATAR)

Address offset: 0x11C + 0x80 * x, (x = 0 to 1)

Reset value: 0x0000 0000

Note: Half-word accesses may be used to read only the MSBs of conversion data.

Reading this register also clears REOCF in DFSDM_FLTxISR.

14.8.9 DFSDM filter x analog watchdog high threshold register

(DFSDM_FLTxAWHTR)

Address offset: 0x120 + 0x80 * x, (x = 0 to 1)

Reset value: 0x0000 0000

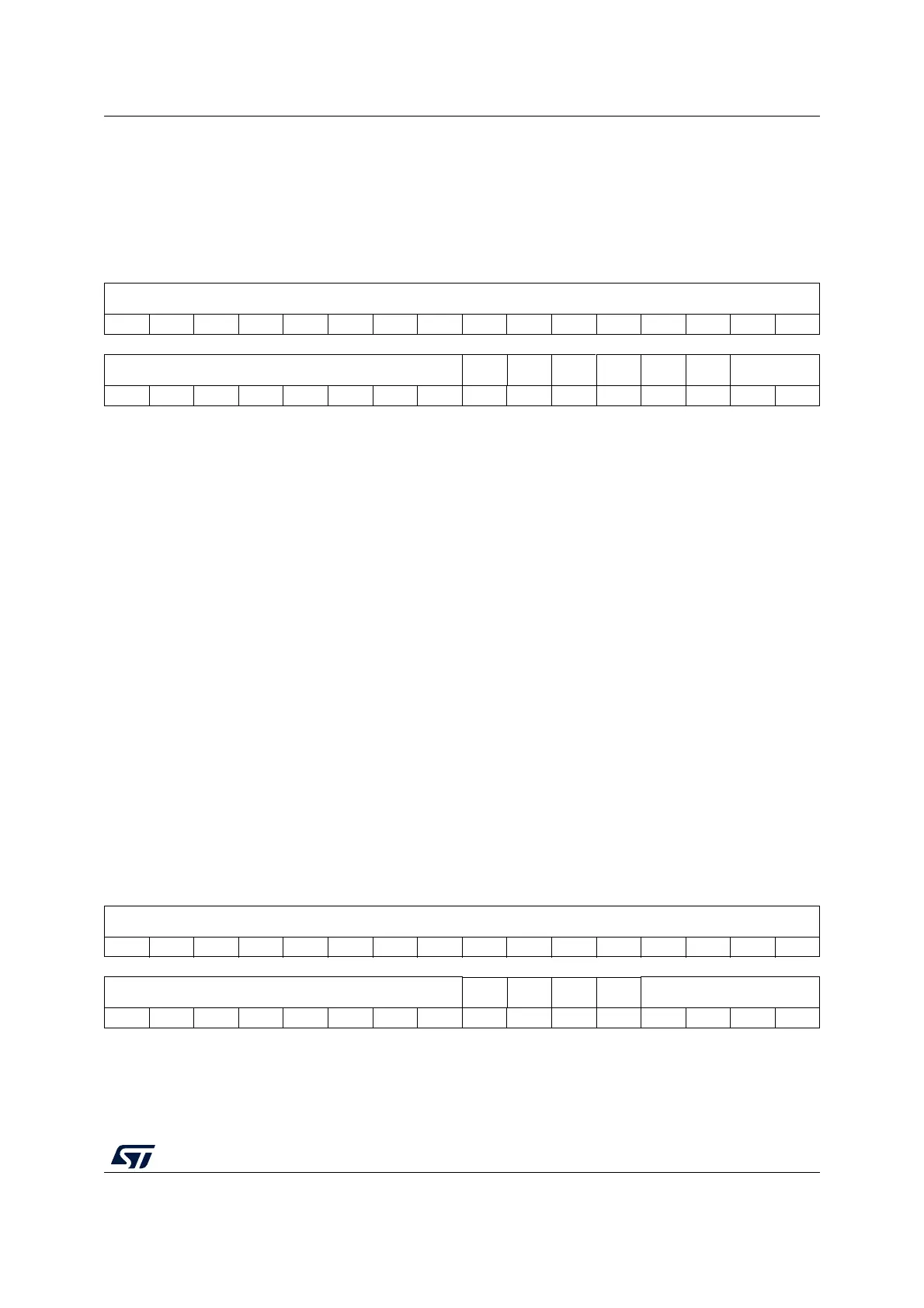

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

RDATA[23:8]

rrrrrrrrrrrrrrrr

1514131211109876543210

RDATA[7:0] Res. Res. Res. RPEND Res. Res. RDATACH[1:0]

rrrrrrrr r rr

Bits 31:8 RDATA[23:0]: Regular channel conversion data

When each regular conversion finishes, its data is stored in this register. The data is valid when

REOCF=1. Reading this register clears the corresponding REOCF.

Bits 7:5 Reserved, must be kept at reset value.

Bit 4 RPEND: Regular channel pending data

Regular data in RDATA[23:0] was delayed due to an injected channel trigger during the conversion

Bits 3:2 Reserved, must be kept at reset value.

Bits 1:0 RDATACH[1:0]: Regular channel most recently converted

When each regular conversion finishes, RDATACH[1:0] is updated to indicate which channel was

converted (because regular channel selection RCH[1:0] in DFSDM_FLTxCR1 register can be

updated during regular conversion). Thus RDATA[23:0] holds the data that corresponds to the

channel indicated by RDATACH[1:0].

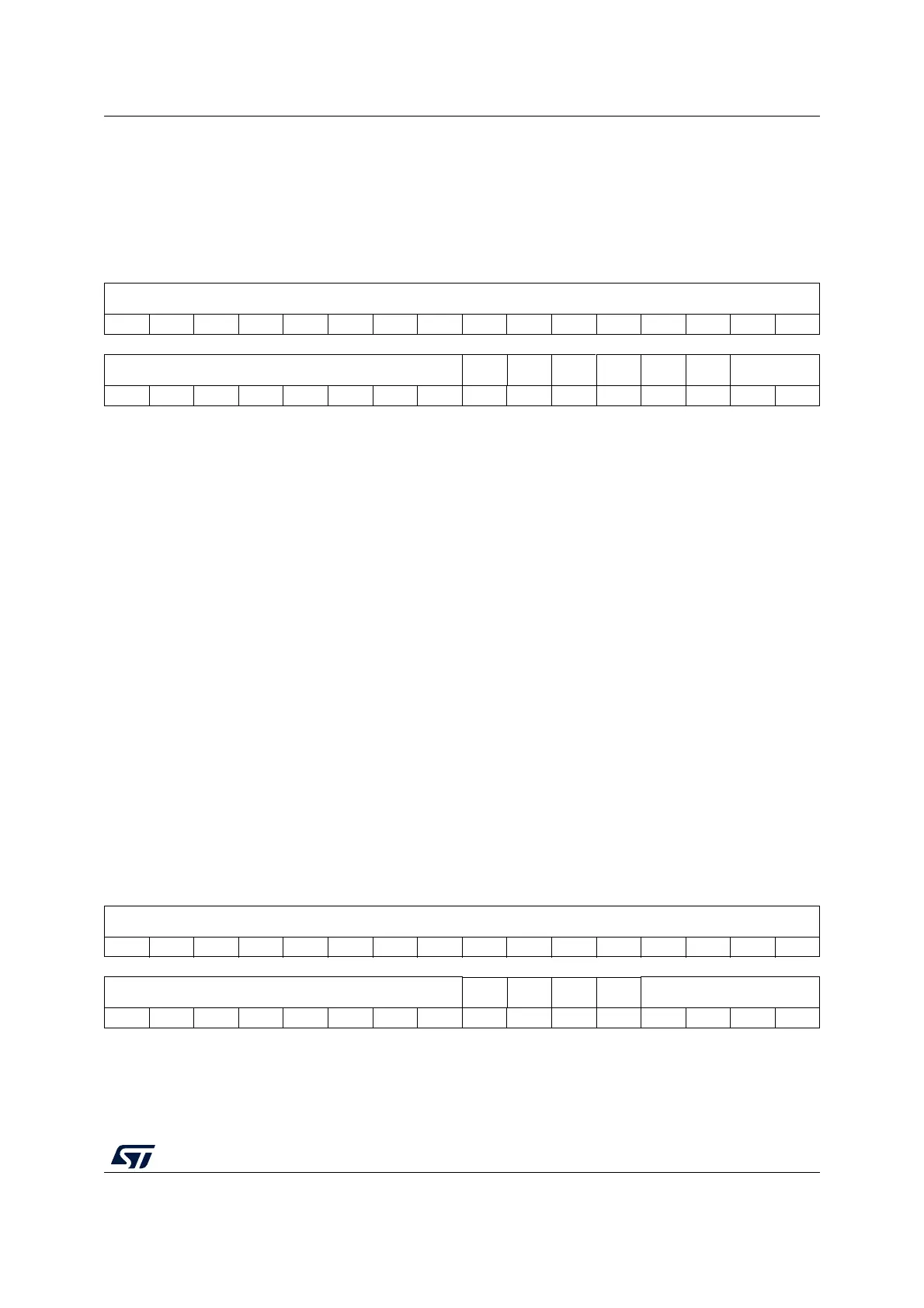

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

AWHT[23:8]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

1514131211109876543210

AWHT[7:0] Res. Res. Res. Res. BKAWH[3:0]

rw rw rw rw rw rw rw rw rw rw rw rw

Loading...

Loading...