Direct memory access controller (DMA) RM0402

198/1163 RM0402 Rev 6

9.3.3 DMA transactions

A DMA transaction consists of a sequence of a given number of data transfers. The number

of data items to be transferred and their width (8-bit, 16-bit or 32-bit) are software-

programmable.

Each DMA transfer consists of three operations:

• a loading from the peripheral data register or a location in memory, addressed through

the DMA_SxPAR or DMA_SxM0AR register

• a storage of the data loaded to the peripheral data register or a location in memory

addressed through the DMA_SxPAR or DMA_SxM0AR register

• a post-decrement of the DMA_SxNDTR register, containing the number of transactions

that still have to be performed

After an event, the peripheral sends a request signal to the DMA controller. The DMA

controller serves the request depending on the channel priorities. As soon as the DMA

controller accesses the peripheral, an Acknowledge signal is sent to the peripheral by the

DMA controller. The peripheral releases its request as soon as it gets the Acknowledge

signal from the DMA controller. Once the request has been deasserted by the peripheral,

the DMA controller releases the Acknowledge signal. If there are more requests, the

peripheral can initiate the next transaction.

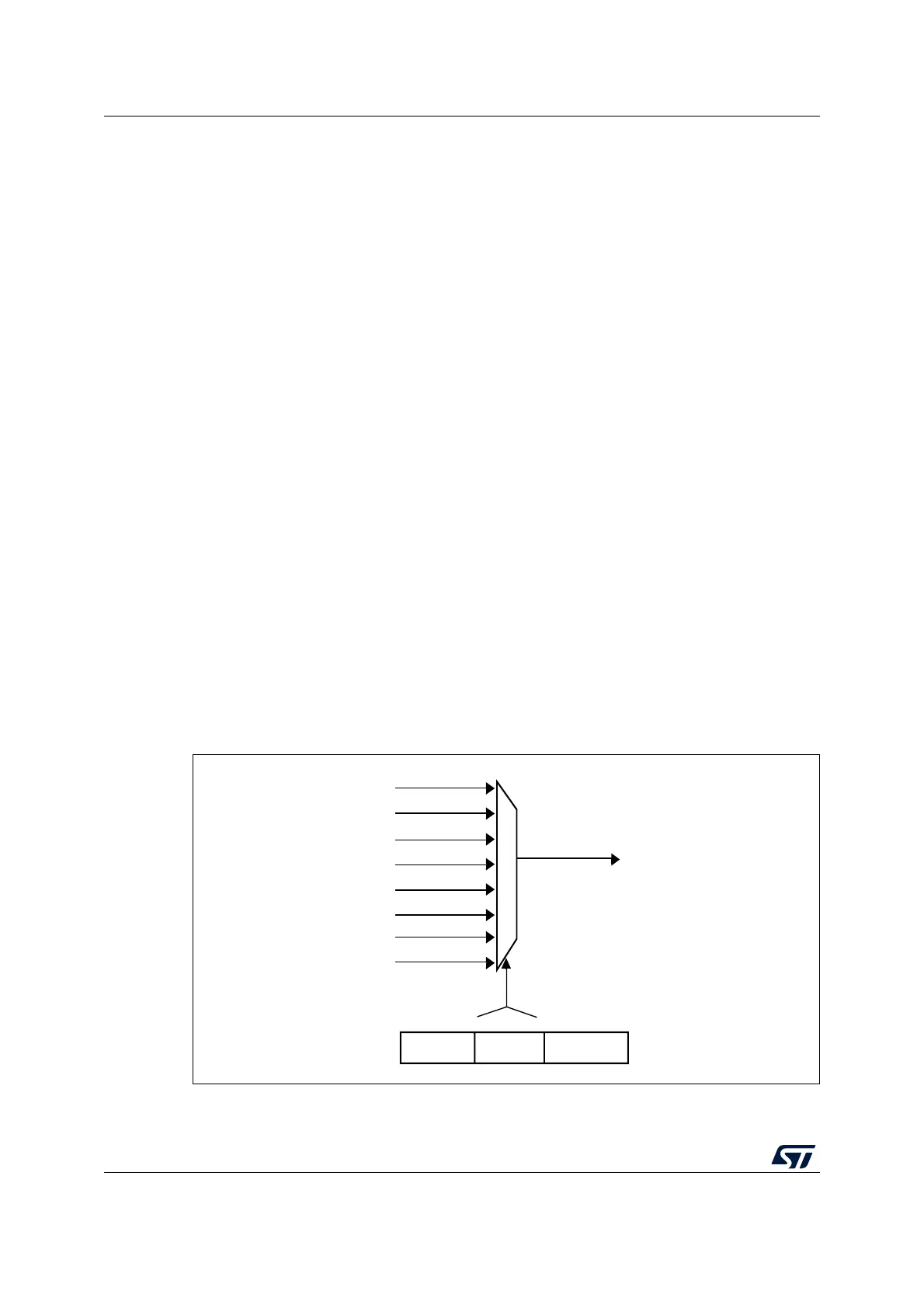

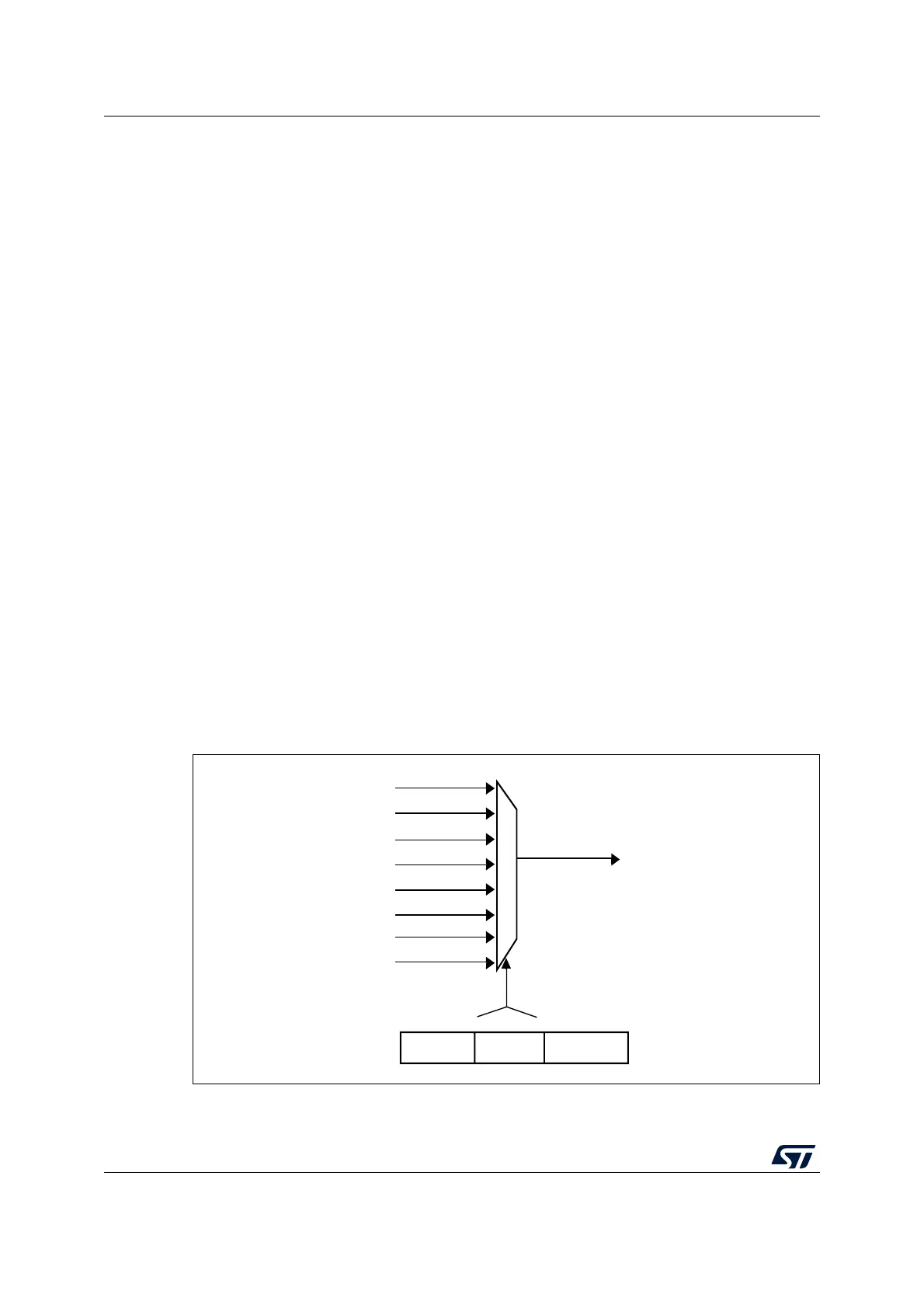

9.3.4 Channel selection

Each stream is associated with a DMA request that can be selected out of 8 possible

channel requests. The selection is controlled by the CHSEL[2:0] bits in the DMA_SxCR

register.

Caution: A same peripheral request can be assigned to two different channels only if the application

ensures that these channels are not requested to be served at the same time. In other

words, if two different channels receive a same asserted peripheral request at the same

time, an unpredictable DMA hardware behavior occurs.

Figure 24. Channel selection

REQ_STREAMx

REQ_STRx_CH7

CHSEL[2:0]

3 1 2 7 25 0

DMA_SxCR

ai15947b

REQ_STRx_CH6

REQ_STRx_CH5

REQ_STRx_CH4

REQ_STRx_CH3

REQ_STRx_CH2

REQ_STRx_CH1

REQ_STRx_CH0

Loading...

Loading...