RM0402 Rev 6 393/1163

RM0402 Digital filter for sigma delta modulators (DFSDM)

400

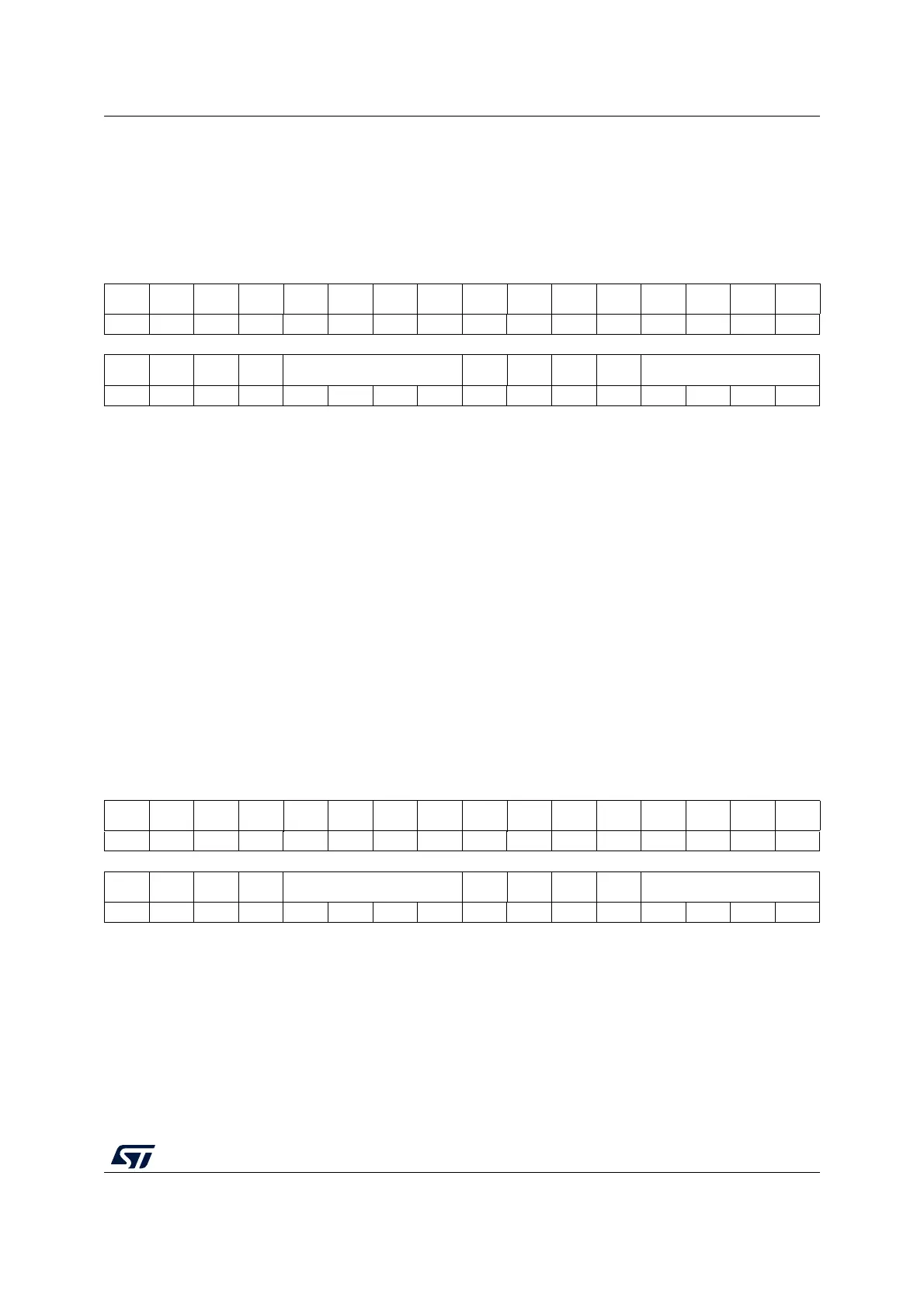

14.8.11 DFSDM filter x analog watchdog status register

(DFSDM_FLTxAWSR)

Address offset: 0x128 + 0x80 * x, (x = 0 to 1)

Reset value: 0x0000 0000

Note: All the bits of DFSDM_FLTxAWSR are automatically reset when DFEN=0.

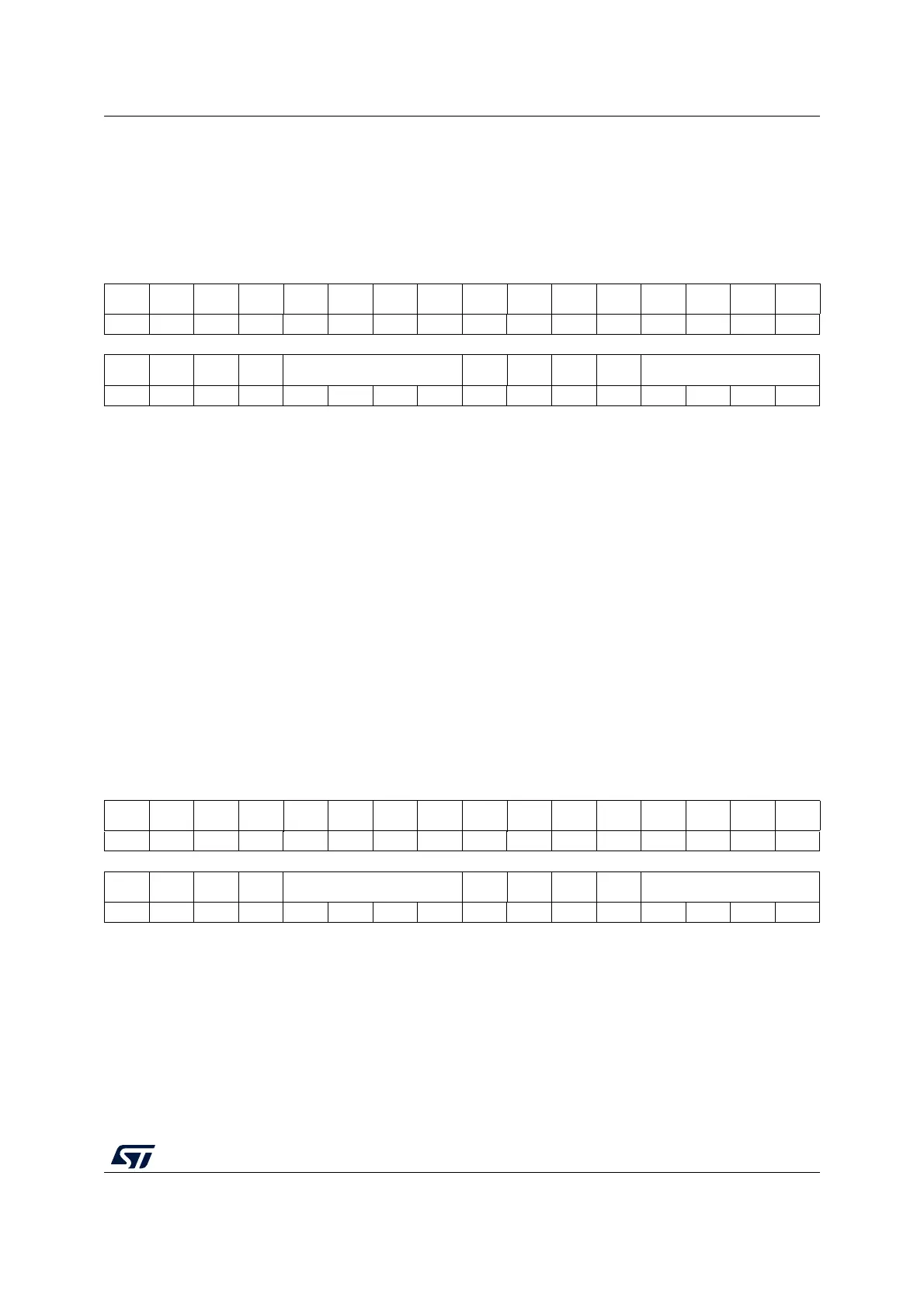

14.8.12 DFSDM filter x analog watchdog clear flag register

(DFSDM_FLTxAWCFR)

Address offset: 0x12C + 0x80 * x, (x = 0 to 1)

Reset value: 0x0000 0000

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. AWHTF[3:0] Res. Res. Res. Res. AWLTF[3:0]

rrrr rrrr

Bits 31:12 Reserved, must be kept at reset value.

Bits 11:8 AWHTF[3:0]: Analog watchdog high threshold flag

AWHTF[y]=1 indicates a high threshold error on channel y. It is set by hardware. It can be cleared by

software using the corresponding CLRAWHTF[y] bit in the DFSDM_FLTxAWCFR register.

Bits 7:4 Reserved, must be kept at reset value.

Bits 3:0 AWLTF[3:0]: Analog watchdog low threshold flag

AWLTF[y]=1 indicates a low threshold error on channel y. It is set by hardware. It can be cleared by

software using the corresponding CLRAWLTF[y] bit in the DFSDM_FLTxAWCFR register.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. CLRAWHTF[3:0] Res. Res. Res. Res. CLRAWLTF[3:0]

rc_w1 rc_w1 rc_w1 rc_w1 rc_w1 rc_w1 rc_w1 rc_w1

Bits 31:12 Reserved, must be kept at reset value.

Loading...

Loading...