USB on-the-go full-speed (OTG_FS) RM0402

1046/1163 RM0402 Rev 6

29.15.41 OTG device V

BUS

pulsing time register

(OTG_DVBUSPULSE)

Address offset: 0x082C

Reset value: 0x0000 05B8

This register specifies the V

BUS

pulsing time during SRP.

29.15.42 OTG device IN endpoint FIFO empty interrupt mask register

(OTG_DIEPEMPMSK)

Address offset: 0x834

Reset value: 0x0000 0000

This register is used to control the IN endpoint FIFO empty interrupt generation

(TXFE_OTG_DIEPINTx).

Bits 31:16 Reserved, must be kept at reset value.

Bits 15:0 VBUSDT[15:0]: Device V

BUS

discharge time

Specifies the V

BUS

discharge time after V

BUS

pulsing during SRP. This value equals:

V

BUS

discharge time in PHY clocks / 1 024

Depending on your V

BUS

load, this value may need adjusting.

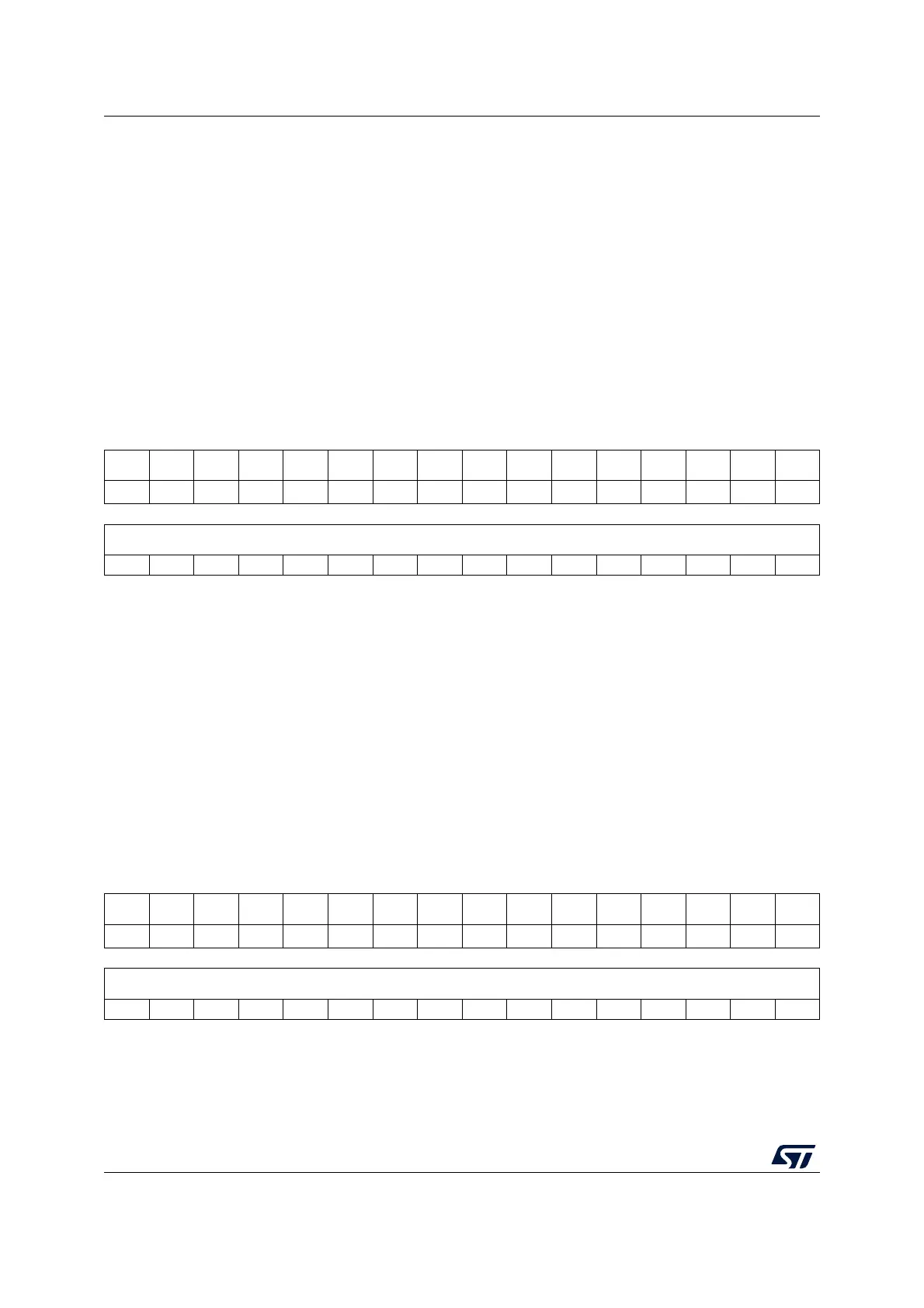

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

DVBUSP[15:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:16 Reserved, must be kept at reset value.

Bits 15:0 DVBUSP[15:0]: Device V

BUS

pulsing time. This feature is only relevant to OTG1.3.

Specifies the V

BUS

pulsing time during SRP. This value equals:

V

BUS

pulsing time in PHY clocks / 1 024

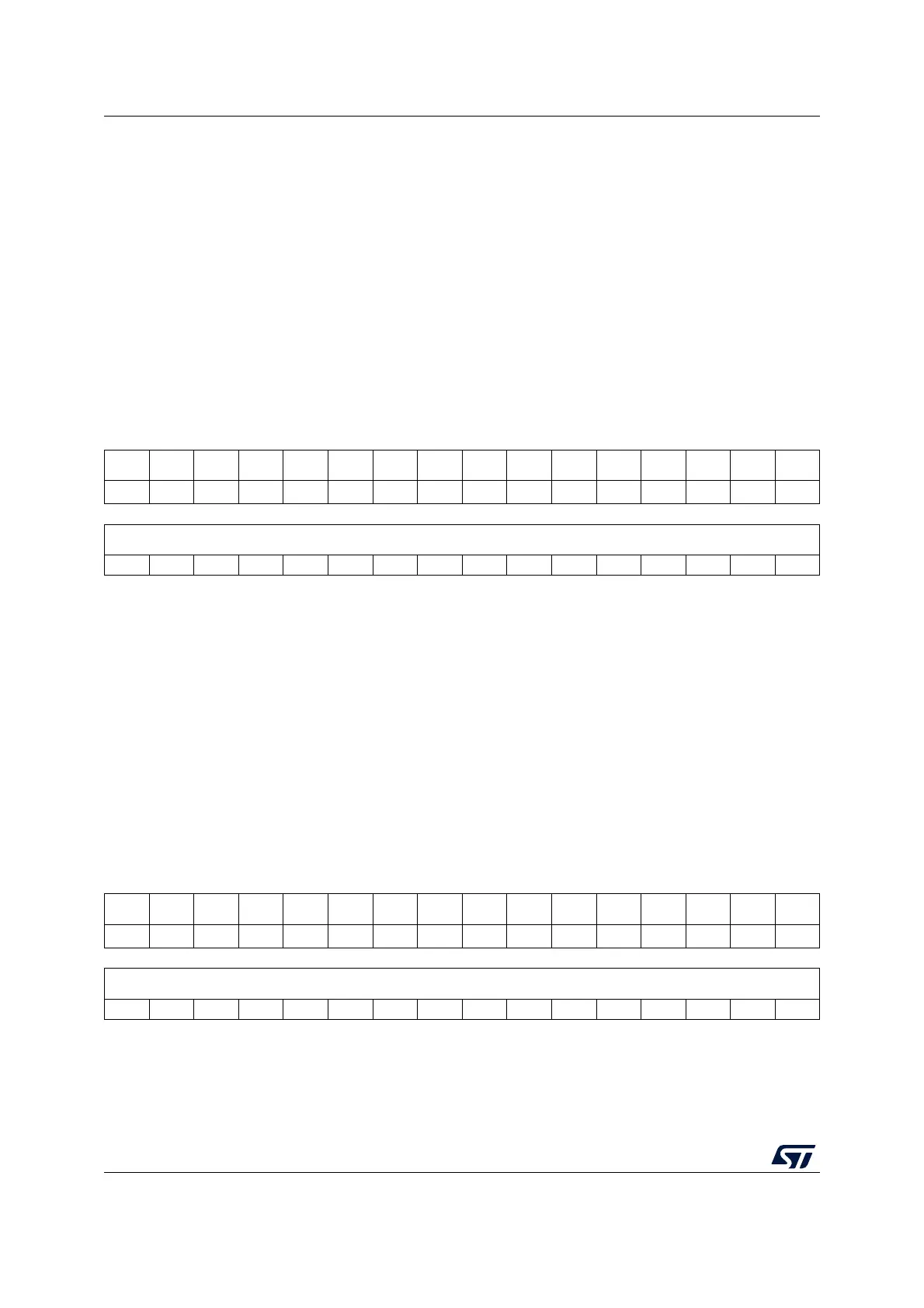

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

INEPTXFEM[15:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Loading...

Loading...