Inter-integrated circuit (I

2

C) interface RM0402

742/1163 RM0402 Rev 6

be set before the ACK of the CRC reception in slave mode. It must be set when

the ACK is set low in master mode.

• A PECERR error flag/interrupt is also available in the I2C_SR1 register.

• If DMA and PEC calculation are both enabled:-

– In transmission: when the I

2

C interface receives an EOT signal from the DMA

controller, it automatically sends a PEC after the last byte.

– In reception: when the I

2

C interface receives an EOT_1 signal from the DMA

controller, it automatically considers the next byte as a PEC and checks it. A DMA

request is generated after PEC reception.

• To allow intermediate PEC transfers, a control bit is available in the I2C_CR2 register

(LAST bit) to determine if it is really the last DMA transfer or not. If it is the last DMA

request for a master receiver, a NACK is automatically sent after the last received byte.

• PEC calculation is corrupted by an arbitration loss.

24.4 I

2

C interrupts

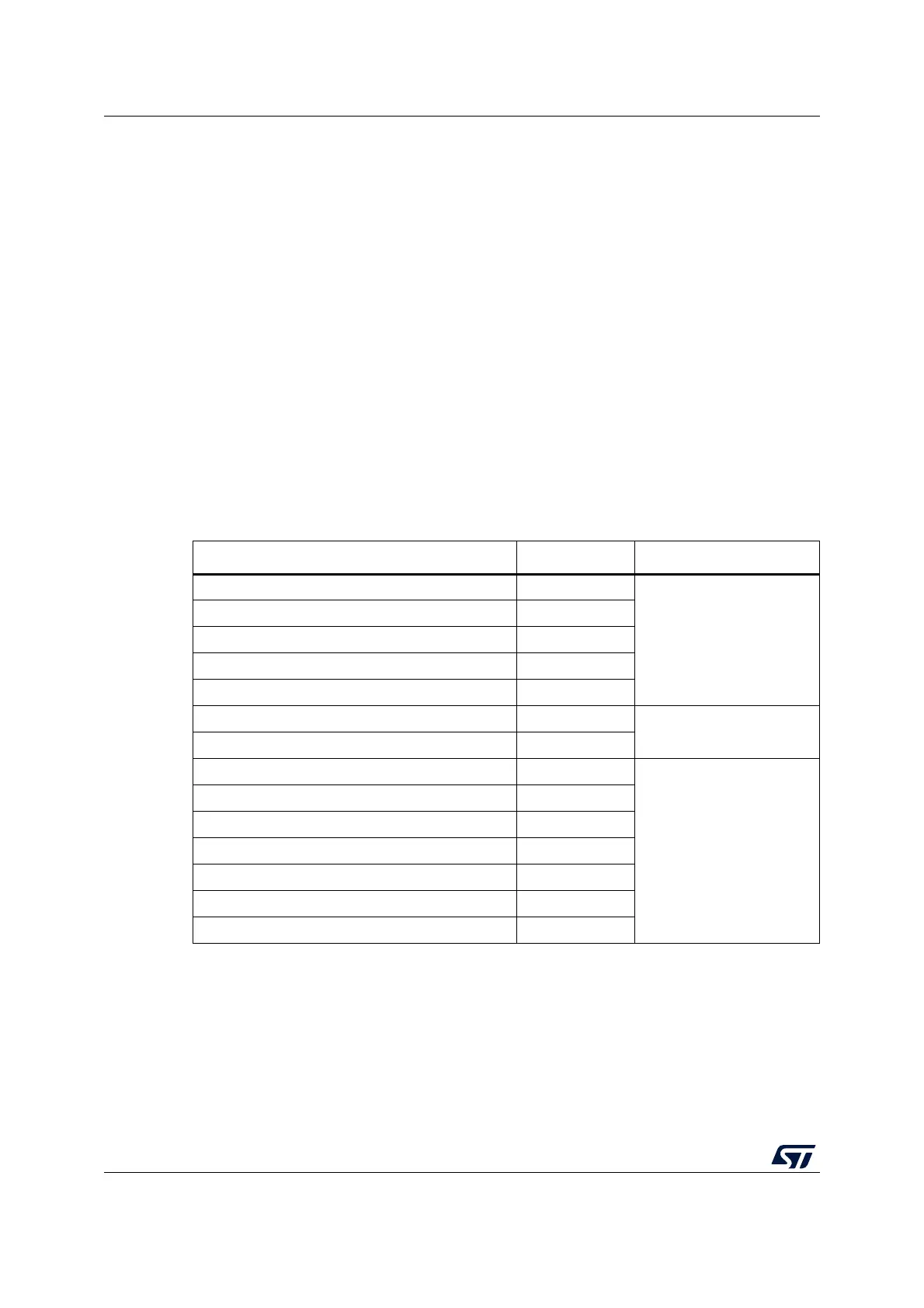

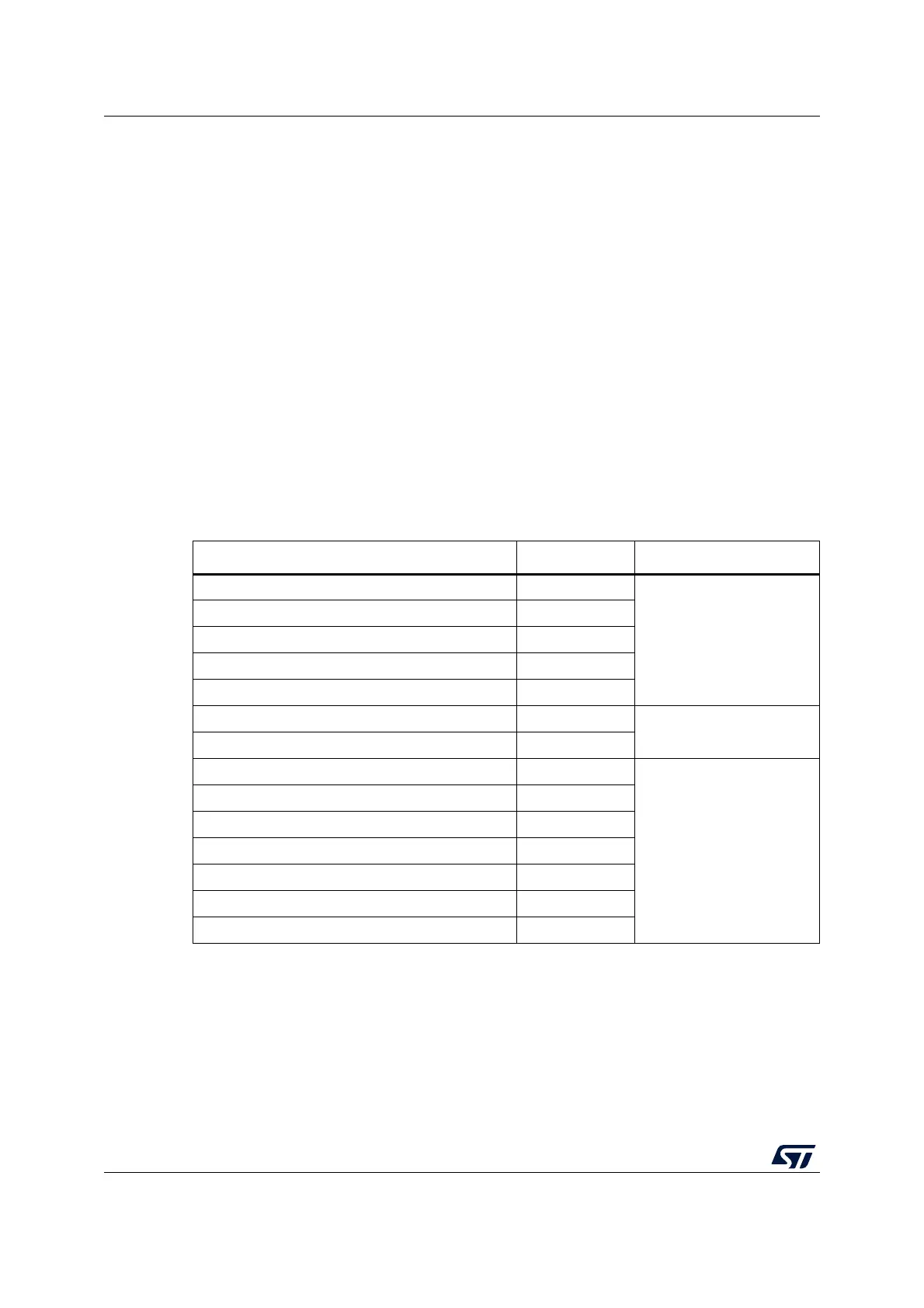

The table below gives the list of I

2

C interrupt requests.

Note: SB, ADDR, ADD10, STOPF, BTF, RxNE and TxE are logically ORed on the same interrupt

channel.

BERR, ARLO, AF, OVR, PECERR, TIMEOUT and SMBALERT are logically ORed on the

same interrupt channel.

Table 134. I

2

C Interrupt requests

Interrupt event Event flag Enable control bit

Start bit sent (Master) SB

ITEVFEN

Address sent (Master) or Address matched (Slave) ADDR

10-bit header sent (Master) ADD10

Stop received (Slave) STOPF

Data byte transfer finished BTF

Receive buffer not empty RxNE

ITEVFEN and ITBUFEN

Transmit buffer empty TxE

Bus error BERR

ITERREN

Arbitration loss (Master) ARLO

Acknowledge failure AF

Overrun/Underrun OVR

PEC error PECERR

Timeout/Tlow error TIMEOUT

SMBus Alert SMBALERT

Loading...

Loading...