Digital filter for sigma delta modulators (DFSDM) RM0402

352/1163 RM0402 Rev 6

1. This example shows 2 DFSDM filters and 4 input channels.

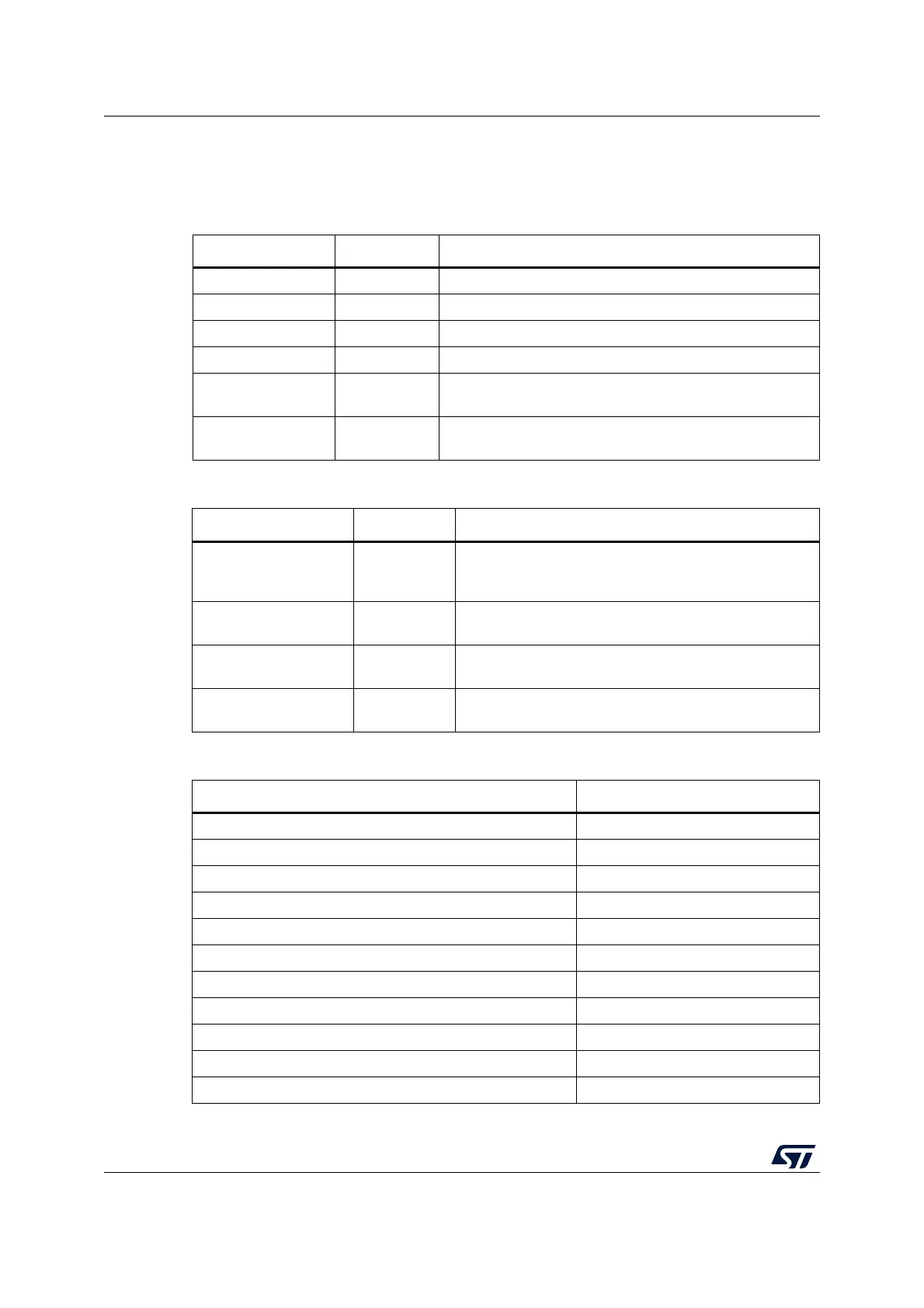

14.4.2 DFSDM pins and internal signals

Table 84. DFSDM external pins

Name Signal Type Remarks

VDD Power supply Digital power supply.

VSS Power supply Digital ground power supply.

CKIN[3:0] Clock input Clock signal provided from external Σ∆ modulator. FT input.

DATIN[3:0] Data input Data signal provided from external Σ∆ modulator. FT input.

CKOUT Clock output

Clock output to provide clock signal into external Σ∆

modulator.

EXTRG[1:0]

External trigger

signal

Input trigger from two EXTI signals to start analog

conversion (from GPIOs: EXTI11, EXTI15).

Table 85. DFSDM internal signals

Name Signal Type Remarks

dfsdm_jtrg[10:0]

Internal/

external trigger

signal

Input trigger from internal/external trigger sources to start

analog conversion, see Table 86 for details.

dfsdm_break[3:0]

break signal

output

Break signals event generation from Analog watchdog or

short-circuit detector

dfsdm_dma[1:0]

DMA request

signal

DMA request signal from each DFSDM_FLTx (x=0..1):

end of injected conversion event.

dfsdm_it[1:0]

Interrupt

request signal

Interrupt signal for each DFSDM_FLTx (x=0..1)

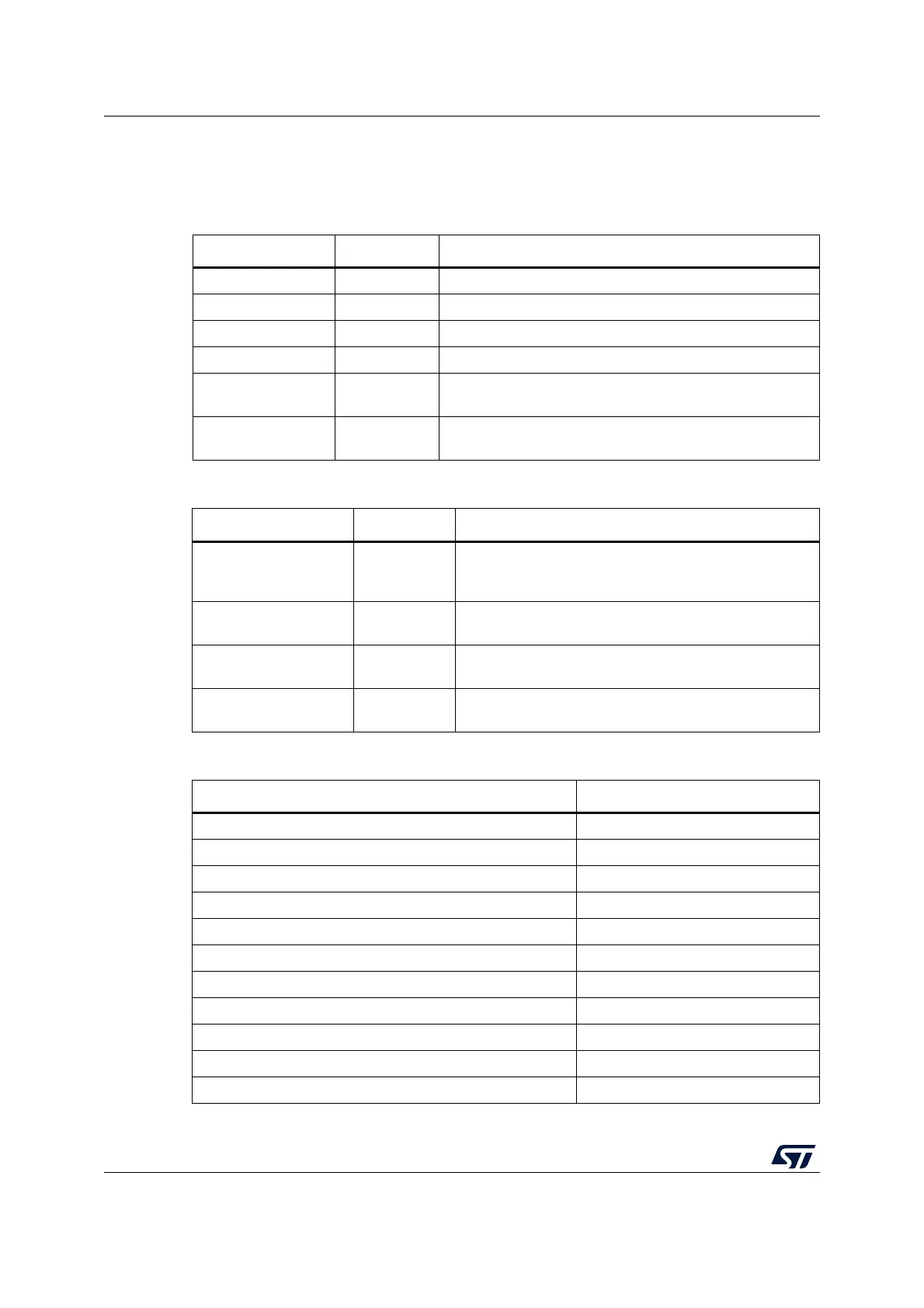

Table 86. DFSDM triggers connection

Trigger name Trigger source

dfsdm_jtrg0 TIM1_TRGO

dfsdm_jtrg1 TIM3_TRGO

dfsdm_jtrg2 TIM8_TRGO

dfsdm_jtrg3 TIM10_OC1

dfsdm_jtrg4 N/A

dfsdm_jtrg5 TIM4_TRGO

dfsdm_jtrg6 N/A

dfsdm_jtrg7 TIM6_TRGO

dfsdm_jtrg8 N/A

dfsdm_jtrg9 EXTI11

dfsdm_jtrg10 EXTI15

Loading...

Loading...