RM0402 Rev 6 289/1163

RM0402 Quad-SPI interface (QUADSPI)

316

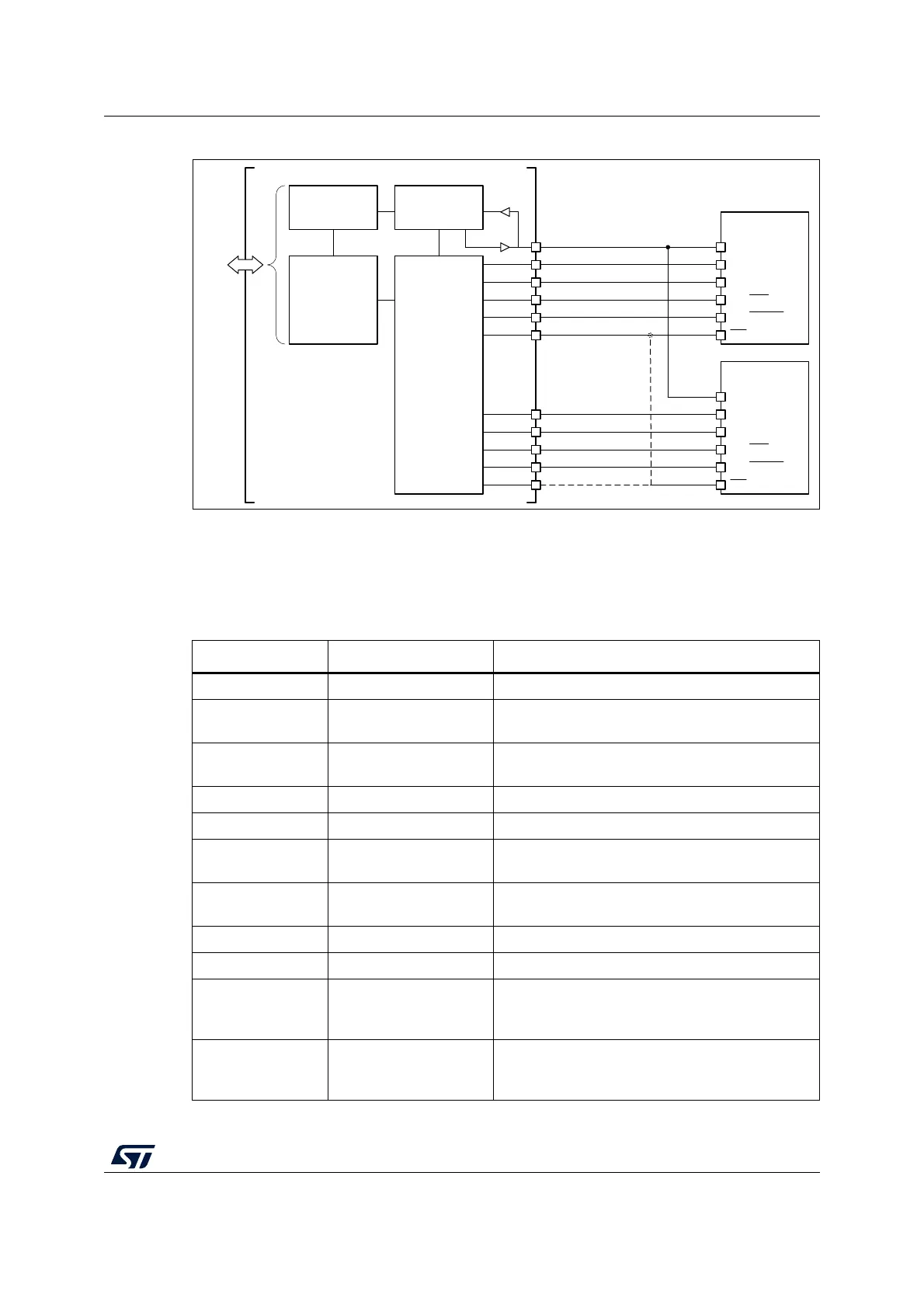

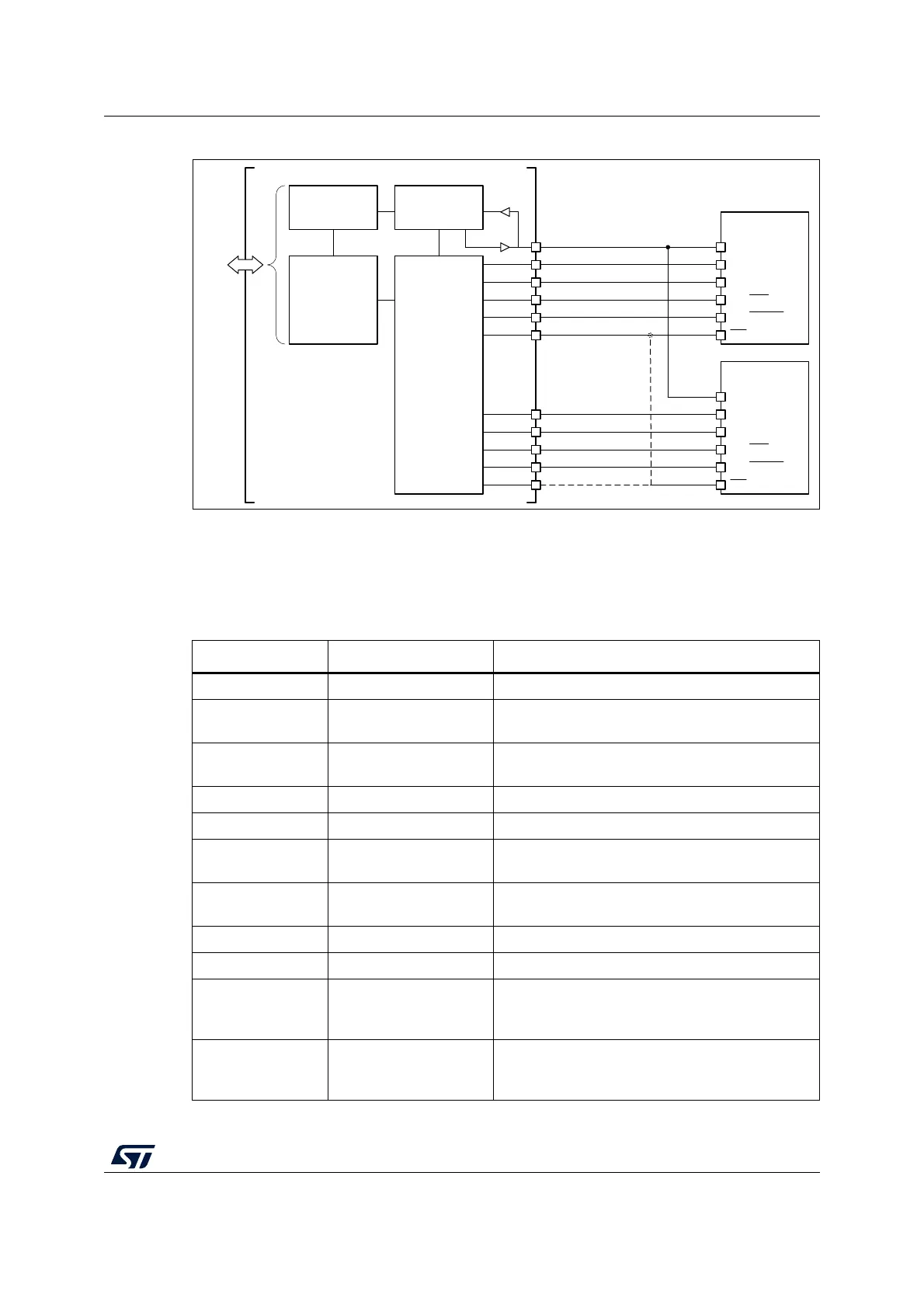

Figure 52. QUADSPI block diagram when dual-flash mode is enabled

12.3.2 QUADSPI pins

Table 71 lists the QUADSPI pins, six for interfacing with a single Flash memory, or 10 to 11

for interfacing with two Flash memories (FLASH 1 and FLASH 2) in dual-flash mode.

MS35316V1

SPI FLASH 1

CLK

BK1_IO0/SO

BK1_IO1/SI

BK1_IO2

BK1_IO3

CLK

Q0/SI

Q1/SO

Q2/WP

Q3/HOLD

BK1_nCS

CS

AHB

Registers /

control

Clock

management

FIFO

Shift register

QUADSPI

BK2_IO0/SO

BK2_IO1/SI

BK2_IO2

BK2_IO3

BK2_nCS

SPI FLASH 2

CLK

Q0/SI

Q1/SO

Q2/WP

Q3/HOLD

CS

Table 71. QUADSPI pins

Signal name Signal type Description

CLK Digital output Clock to FLASH 1 and FLASH 2

BK1_IO0/SO Digital input/output

Bidirectional IO in dual/quad modes or serial output

in single mode, for FLASH 1

BK1_IO1/SI Digital input/output

Bidirectional IO in dual/quad modes or serial input

in single mode, for FLASH 1

BK1_IO2 Digital input/output Bidirectional IO in quad mode, for FLASH 1

BK1_IO3 Digital input/output Bidirectional IO in quad mode, for FLASH 1

BK2_IO0/SO Digital input/output

Bidirectional IO in dual/quad modes or serial output

in single mode, for FLASH 2

BK2_IO1/SI Digital input/output

Bidirectional IO in dual/quad modes or serial input

in single mode, for FLASH 2

BK2_IO2 Digital input/output Bidirectional IO in quad mode, for FLASH 2

BK2_IO3 Digital input/output Bidirectional IO in quad mode, for FLASH 2

BK1_nCS Digital output

Chip select (active low) for FLASH 1. Can also be

used for FLASH 2 if QUADSPI is always used in

dual-flash mode.

BK2_nCS Digital output

Chip select (active low) for FLASH 2. Can also be

used for FLASH 1 if QUADSPI is always used in

dual-flash mode.

Loading...

Loading...