MPC5604B/C Microcontroller Reference Manual, Rev. 8

Freescale Semiconductor 357

All registers are accessible via 8-bit, 16-bit or 32-bit accesses. However, 16-bit accesses must be aligned

to 16-bit boundaries, and 32-bit accesses must be aligned to 32-bit boundaries. As an example, the IBDF

register for the frequency divider is accessible by a 16-bit read/write to address Base + 0x000, but

performing a 16-bit access to Base + 0x001 is illegal.

20.3.2 I

2

C Bus Address Register (IBAD)

This register contains the address the I

2

C bus will respond to when addressed as a slave; note that it is not

the address sent on the bus during the address transfer.

Table 20-1. I2C memory map

Base address: 0xFFE3_0000

Address offset Register Location

0x0 I

2

C Bus Address Register (IBAD) on page 357

0x1 I

2

C Bus Frequency Divider Register (IBFD) on page 358

0x2 I

2

C Bus Control Register (IBCR) on page 364

0x3 I

2

C Bus Status Register (IBSR) on page 365

0x4 I

2

C Bus Data I/O Register (IBDR) on page 366

0x5 I

2

C Bus Interrupt Config Register (IBIC) on page 367

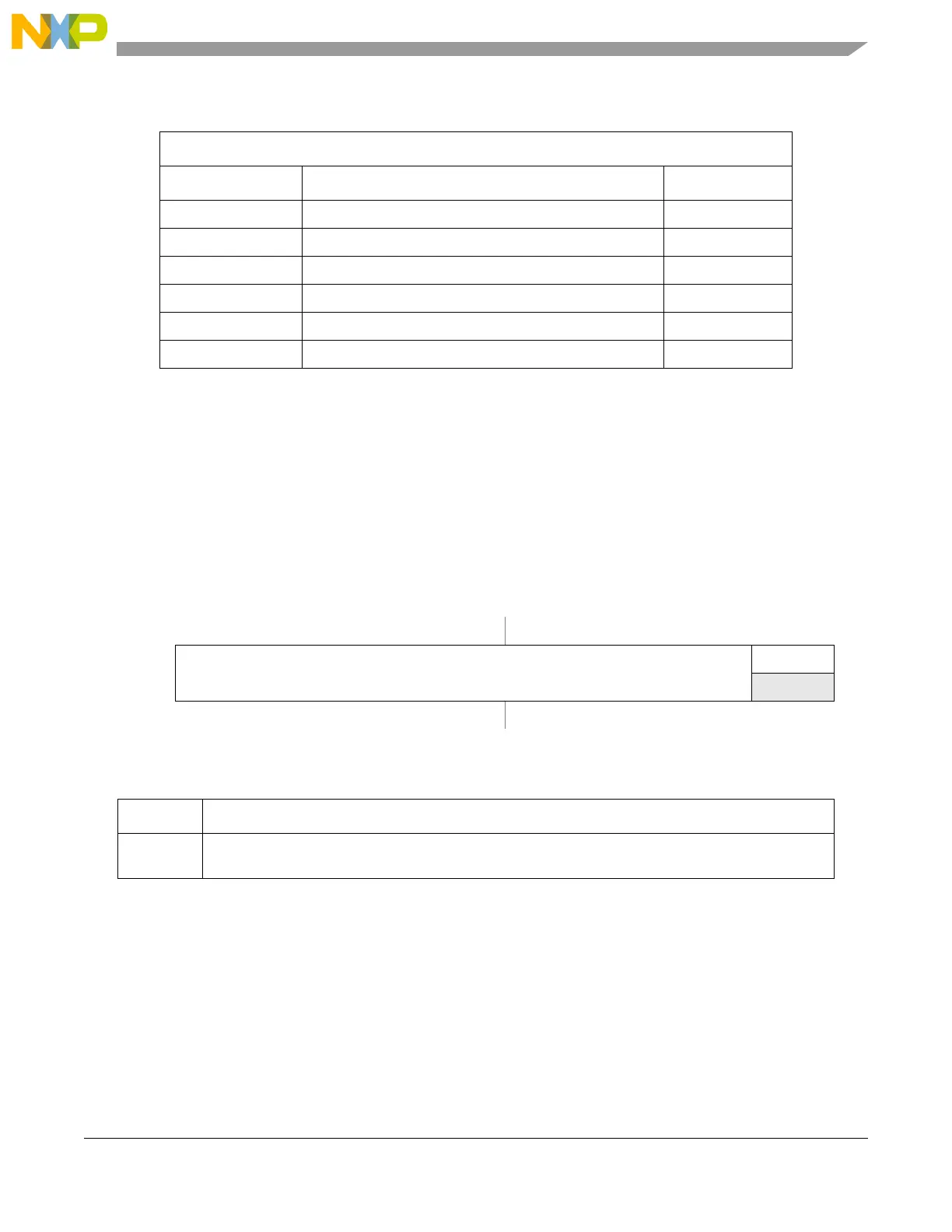

Offset 0x0 Access: Read/write any time

76543210

R

ADR

0

W

Reset00000000

Figure 20-2. I

2

C Bus Address Register (IBAD)

Table 20-2. IBAD field descriptions

Field Description

ADR Slave Address. Specific slave address to be used by the I

2

C Bus module.

Note: The default mode of I

2

C Bus is slave mode for an address match on the bus.

Loading...

Loading...