Virtex-5 FPGA User Guide www.xilinx.com 109

UG190 (v5.0) June 19, 2009

Application Guidelines

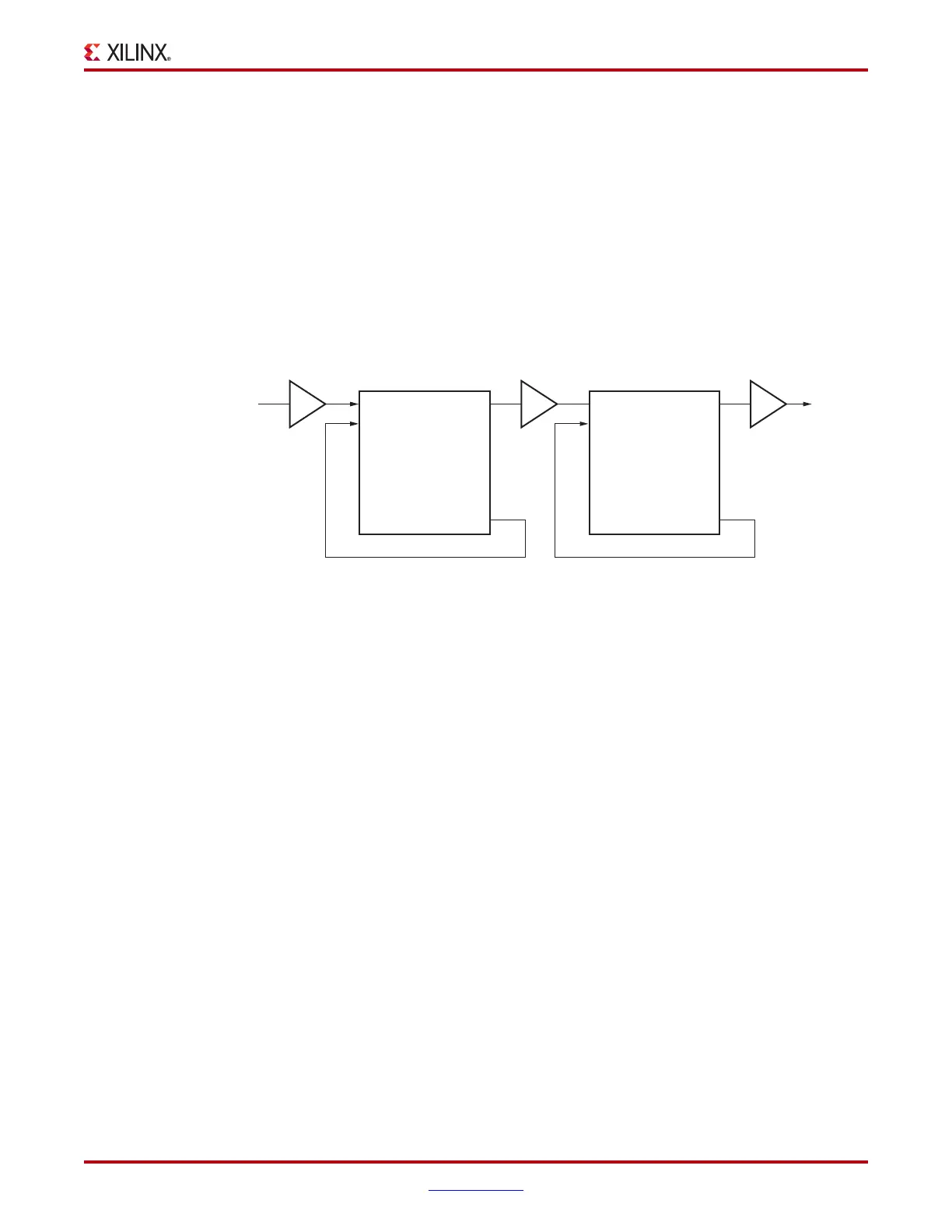

PLL to PLL Connection

The PLL can be cascaded to allow generation of a greater range of clock frequencies. The

frequency range restrictions still apply. Equation 3-9 shows the relationship between the

final output frequency and the input frequency and counter settings of the two PLLs

(Figure 3-15.) The phase relationship between the output clock of the second PLL and the

input clock is undefined.To cascade PLLs, route the output of the first PLL to a BUFG and

then to the CLKIN pin of the second PLL. This path provides the lowest device jitter.

Equation 3-9

Application Guidelines

This section summarizes when to select a DCM over a PLL, or a PLL over a DCM.

Virtex-5 FPGA PLLs support up to six independent outputs. Designs using several

different outputs should use PLLs. An example of designs using several different outputs

follows. The PLL is an ideal solution for this type of application because it can generate a

configurable set of outputs over a wide range while the DCM has a fixed number of

predetermined outputs based off the reference clock. When the application requires a fine

phase shift or a dynamic variable phase shift, a DCM could be a better solution.

X-Ref Target - Figure 3-15

Figure 3-15: Cascading Two PLLs

f

OUTPLL2

f

OUTPLL1

M

PLL2

D

PLL2

O

PLL2

×

----------------------------------------

f

IN

M

PLL1

D

PLL1

O

PLL1

×

----------------------------------------

M

PLL2

D

PLL2

O

PLL2

×

----------------------------------------

×==

CLKIN1

CLKFBIN

RST

CLKOUT0

CLKOUT1

CLKOUT2

CLKOUT3

CLKOUT4

CLKOUT5

CLKFBOUT

CLKIN1

CLKFBIN

RST

PLLPLL

CLKOUT0

To Lo g i c

IBUFG BUFG BUFG

CLKOUT1

CLKOUT2

CLKOUT3

CLKOUT4

CLKOUT5

CLKFBOUT

ug190_3_16_032506

Loading...

Loading...