Virtex-5 FPGA User Guide www.xilinx.com 141

UG190 (v5.0) June 19, 2009

Built-in FIFO Support

Synchronous FIFO Implementations

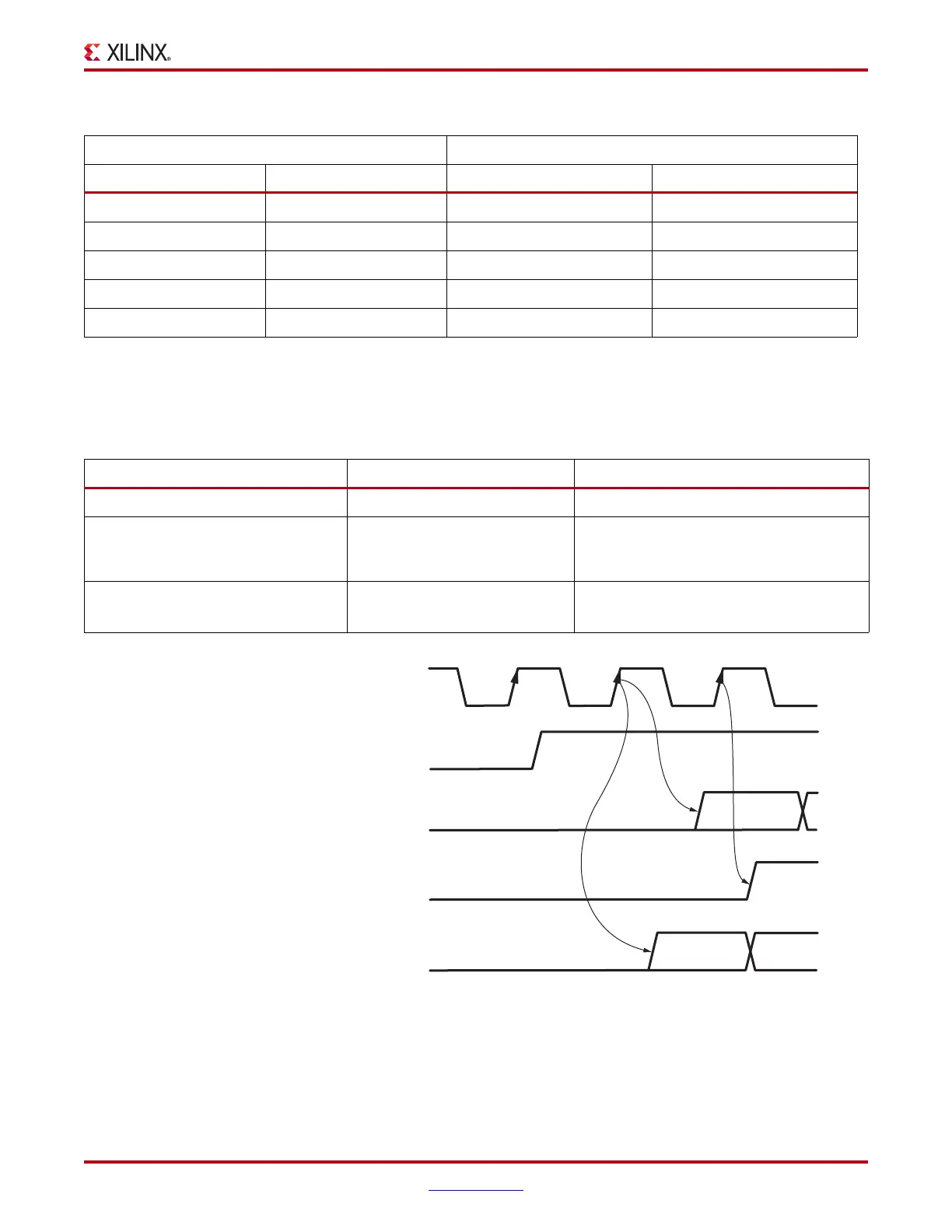

Table 4-14 outlines varied implementations of synchronous FIFOs. Figure 4-16 shows the

timing differences.

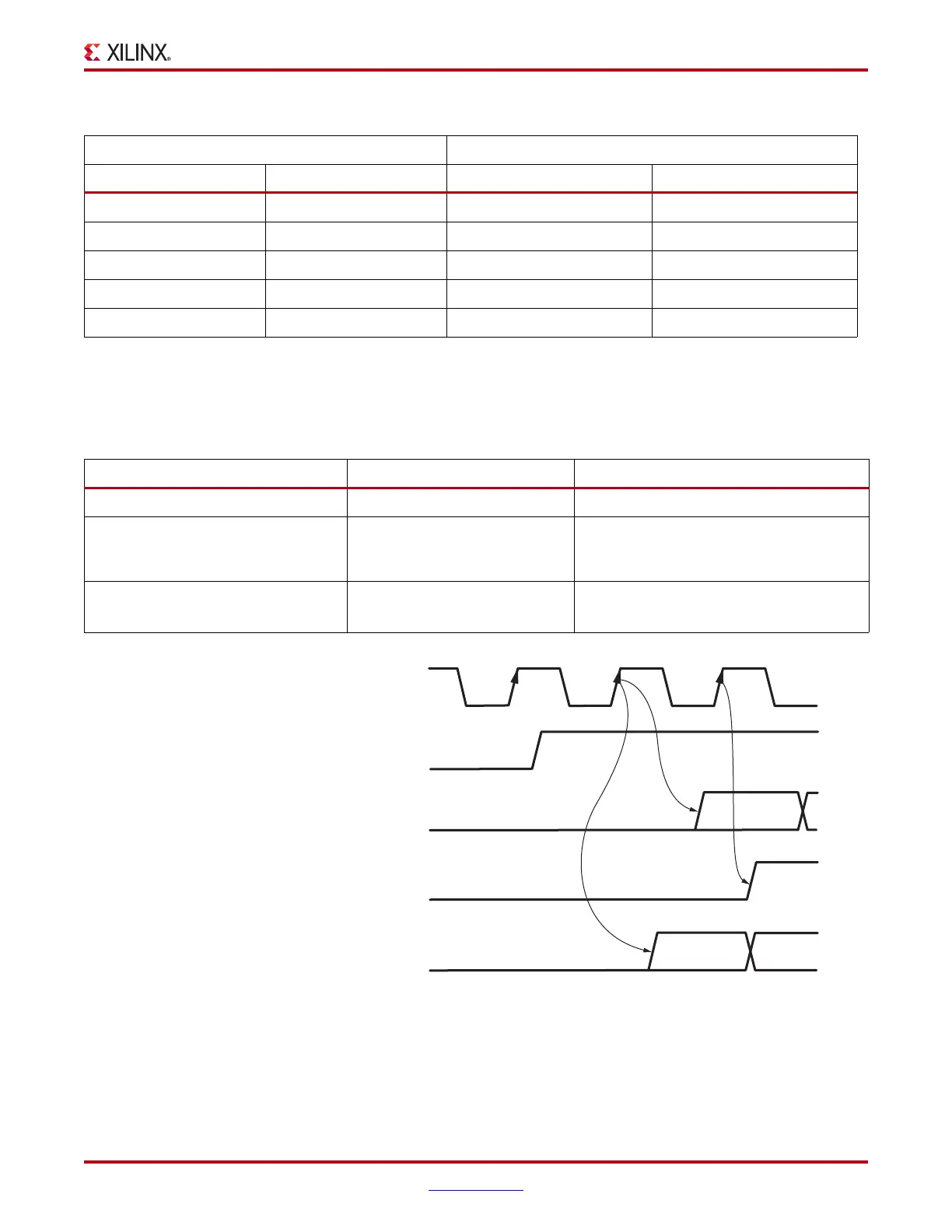

Table 4-13: FIFO Capacity

Standard Mode FWFT Mode

18 Kb FIFO 36 Kb FIFO 18 Kb FIFO 36 Kb FIFO

4k + 1 entries by 4 bits 8k + 1 entries by 4 bits 4k + 2 entries by 4 bits 8k + 2 entries by 4 bits

2k + 1 entries by 9 bits 4k + 1 entries by 9 bits 2k + 2 entries by 9 bits 4k + 2 entries by 9 bits

1k + 1 entries by 18 bits 2k + 1 entries by 18 bits 1k + 2 entries by 18 bits 2k + 2 entries by 18 bits

512 + 1 entries by 36 bits 1k + 1 entries by 36 bits 512 + 2 entries by 36 bits 1k + 2 entries by 36 bits

512 + 1 entries by 72 bits 512 + 2 entries by 72 bits

Table 4-14: Comparison of Synchronous FIFO Implementations

Synchronous FIFO Implementations Advantages Disadvantages

EN_SYN = TRUE, DO_REG = 0 No flag uncertainty Longer clock-to-out signals

EN_SYN = TRUE, DO_REG = 1 Faster clock-to-out signals, no

flag uncertainty

Data Latency increased by one. Behaves

like a synchronous FIFO with an extra data

output pipeline register

EN_SYN = FALSE, DO_REG = 1

RDCLK = WRCLK

Faster clock-to-out signals.

Similar to a Virtex-4 FIFO.

Falling-edge flag uncertainty. Rising-edge

guaranteed on FULL and EMPTY

X-Ref Target - Figure 4-16

Figure 4-16: Synchronous FIFO Data Timing Diagram

ug190_c4_x1_071007

rdclk

rden

DO

EN_SYN = TRUE

DO_REG = 0

DO

EN_SYN = TRUE

DO_REG = 1

DO

EN_SYN = FALSE

DO_REG = 1

T

CKO

= 1.9ns

Loading...

Loading...