126 www.xilinx.com Virtex-5 FPGA User Guide

UG190 (v5.0) June 19, 2009

Chapter 4: Block RAM

For cascadable block RAM using the RAMB36, the data width is one bit, and the address

bus is 16 bits <15:0>. The address bit 15 is only used in cascadable block RAM. For non-

cascading block RAM, connect High.

Data and address pin mapping is further described in the “Additional RAMB18 and

RAMB36 Primitive Design Considerations”section.

Data-In Buses - DI[A|B]<#:0> & DIP[A|B]<#:0>

Data-in buses provide the new data value to be written into RAM. The regular data-in bus

(DI), plus the parity data-in bus (DIP) when available, have a total width equal to the port

width. For example the 36-bit port data width is represented by DI<31:0> and DIP<3:0>, as

shown in Table 4-6 and Table 4-7.

Data-Out Buses - DO[A|B]<#:0> and DOP[A|B]<#:0>

Data-out buses reflect the contents of memory cells referenced by the address bus at the

last active clock edge during a read operation. During a write operation (WRITE_FIRST or

READ_FIRST configuration), the data-out buses reflect either the data being written or the

stored value before write. During a write operation in NO_CHANGE mode, data-out

buses are not changed. The regular data-out bus (DO) plus the parity data-out bus (DOP)

(when available) have a total width equal to the port width, as shown in Table 4-6 and

Table 4-7.

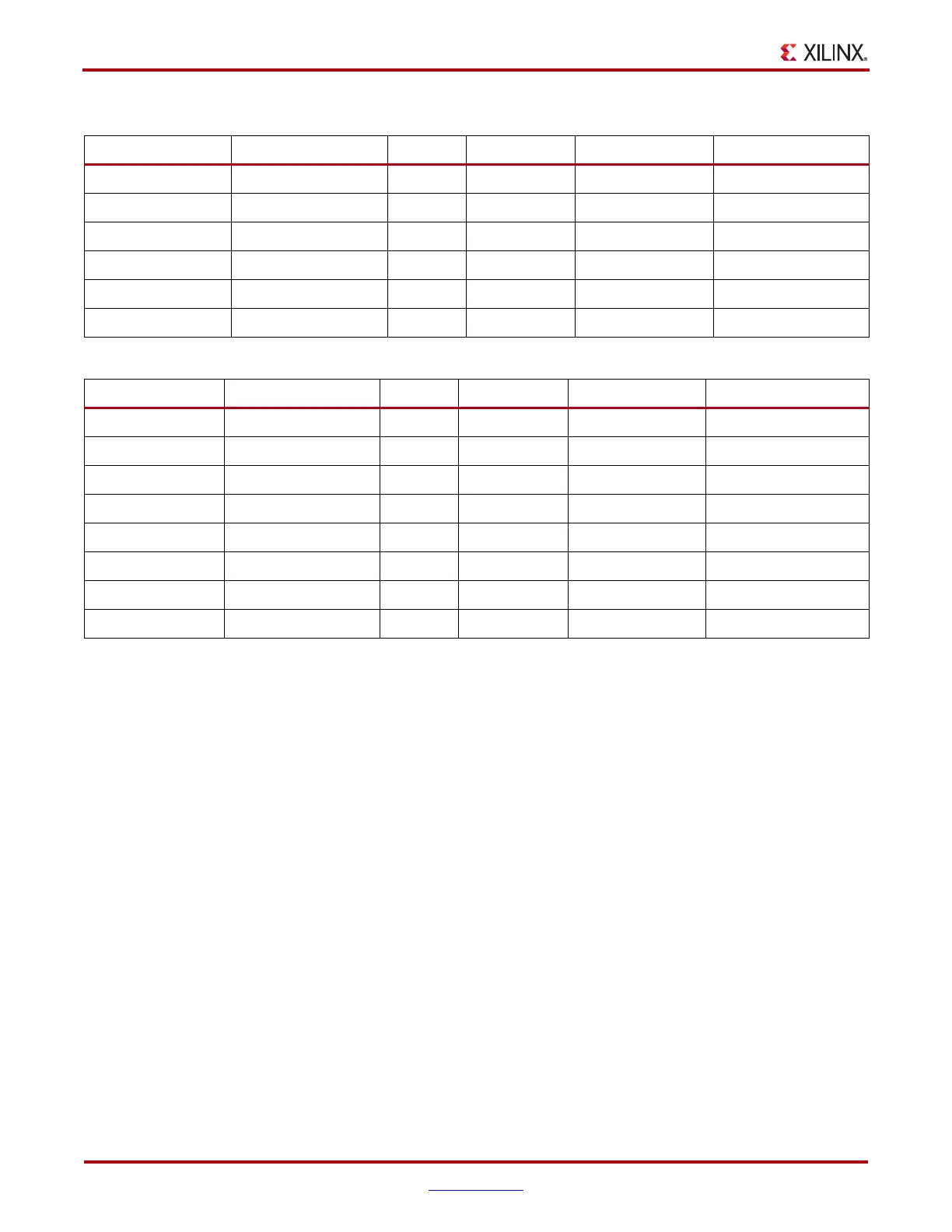

Table 4-6: Port Aspect Ratio for RAMB18 and RAMB18SDP

Port Data Width Port Address Width Depth ADDR Bus DI Bus / DO Bus DIP Bus / DOP Bus

1 14 16,384 <13:0> <0> NA

2 13 8,192 <13:1> <1:0> NA

4 12 4,096 <13:2> <3:0> NA

9 11 2,048 <13:3> <7:0> <0>

18 10 1,024 <13:4> <15:0> <1:0>

36 (RAMB18SDP) 9 512 <13:5> <31:0> <3:0>

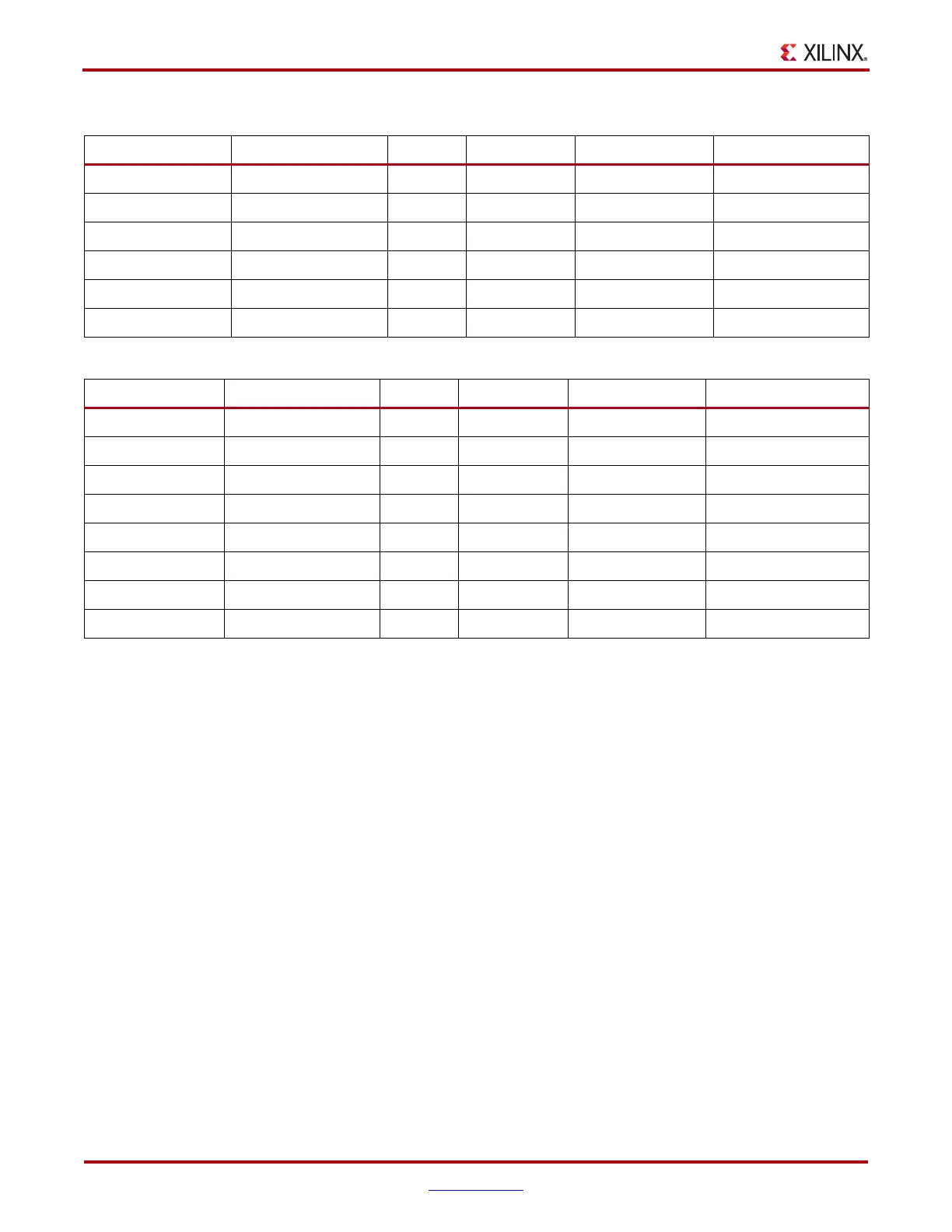

Table 4-7: Port Aspect Ratio for RAMB36

Port Data Width Port Address Width Depth ADDR Bus DI Bus / DO Bus DIP Bus / DOP Bus

1 15 32,768 <14:0> <0> NA

2 14 16,384 <14:1> <1:0> NA

4 13 8,192 <14:2> <3:0> NA

9 12 4,096 <14:3> <7:0> <0>

18 11 2,048 <14:4> <15:0> <1:0>

36 10 1,024 <14:5> <31:0> <3:0>

72 (RAMB36SDP) 9 512 <14:6> <63:0> <7:0>

1 (Cascade) 16 65536 <15:0> <0> NA

Loading...

Loading...