Virtex-5 FPGA User Guide www.xilinx.com 157

UG190 (v5.0) June 19, 2009

FIFO Applications

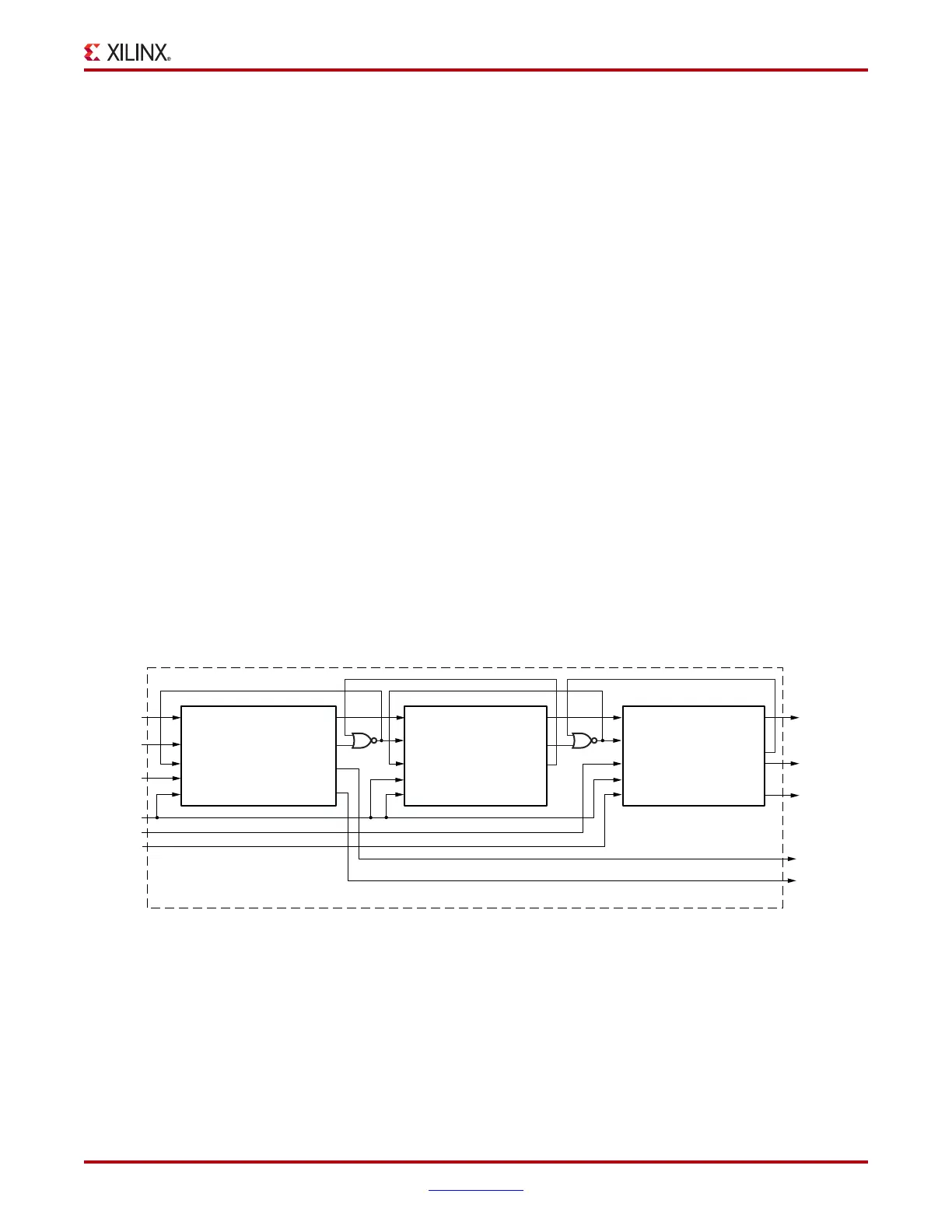

Case 6: Simultaneous Read and Write for Multirate FIFO

Simultaneous read and write operations for an asynchronous FIFO is not deterministic

when the FIFO is at the condition to assert a status flag. The FIFO logic resolves the

situation (either assert or not assert the flag), the software simulation model can not reflect

this behavior and mismatch can occur. When using a single clock for RDCLK and WRCLK,

use the FIFO in synchronous mode (EN_SYN=TRUE).

FIFO Applications

A FIFO larger than a single Virtex-5 FPGA FIFO block can be created by:

• Cascading two or more FIFOs to form a deeper FIFO.

• Building a wider FIFO by connecting two or more FIFOs in parallel.

Cascading FIFOs to Increase Depth

Figure 4-26 shows a way of cascading N FIFO36s to increase depth. The application sets

the first N–1 FIFOs in FWFT mode and uses external resources to connect them together.

The data latency of this application is the sum of the individual FIFO latencies. The

maximum frequency is limited by the feedback path. The NOR gate is implemented using

CLB logic.

• N can be 2 or more; if N is 2, the middle FIFOs are not needed.

• If WRCLK is faster than RDCLK, then INTCLK = WRCLK

• If WRCLK is equal to or slower than RDCLK, then INTCLK = RDCLK

• ALMOST_EMPTY threshold is set in the Nth FIFO; ALMOST_FULL threshold is set

in 1st FIFO.

X-Ref Target - Figure 4-26

Figure 4-26: Example: Cascading Multiple FIFOs by Depth

ug190_4_23_090407

DO<3:0>

ALMOST

EMPTY

EMPTY

ALMOST

EMPTY

EMPTY

ALMOSTFULL

FULL

RDCLK

WRCLK

DI<3:0>

DO<3:0>

RDEN

WREN

DI<3:0>

RDEN

RDCLK

WREN

WRCLK

RDCLK

WRCLK

DI<3:0>

DO<3:0>

FULL

RDEN

WREN

INTCLK

N x 8K x 4 FIFO

EMPTY

FIFO 1

FWFT

Mode

RDCLK

WRCLK

DI<3:0>

DO<3:0>

RDEN

WREN

EMPTY

FULL

FIFO 2 ... (N–1)

FWFT

Mode

FIFO N

ALMOST

FULL

FULL

Loading...

Loading...