Virtex-5 FPGA User Guide www.xilinx.com 149

UG190 (v5.0) June 19, 2009

FIFO VHDL and Verilog Templates

Similarly, the ALMOST_EMPTY flag can be used to stop reading. However, this would

make it impossible to read the very last entries remaining in the FIFO. The user can ignore

the Almost Empty signal and continue to read until EMPTY is asserted.

The Almost Full and Almost Empty offsets can also be used in unstoppable block transfer

applications to signal that a complete block of data can be written or read.

When setting the offset ranges in the design tools, use hexadecimal notation.

FIFO VHDL and Verilog Templates

VHDL and Verilog templates are available in the Libraries Guide.

FIFO Timing Models and Parameters

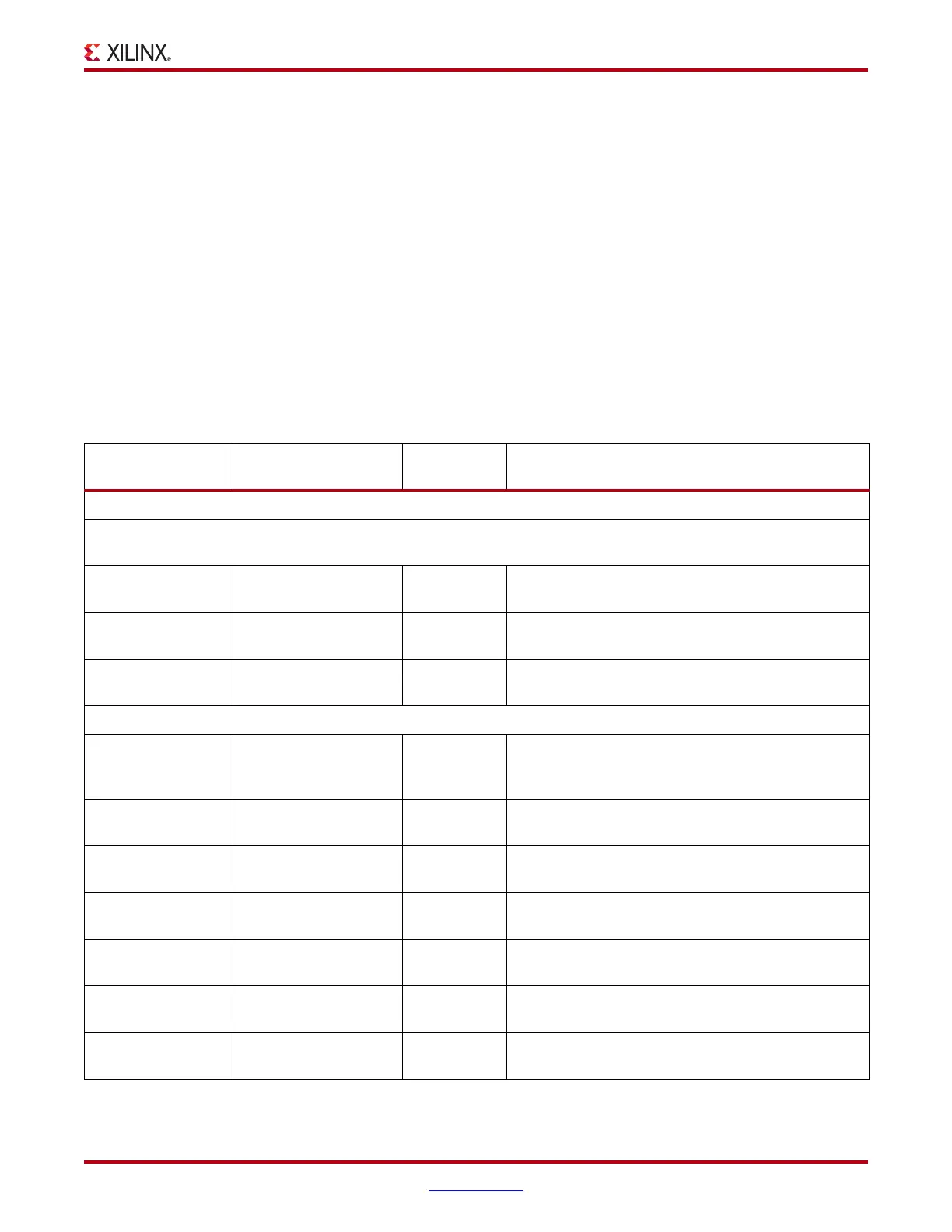

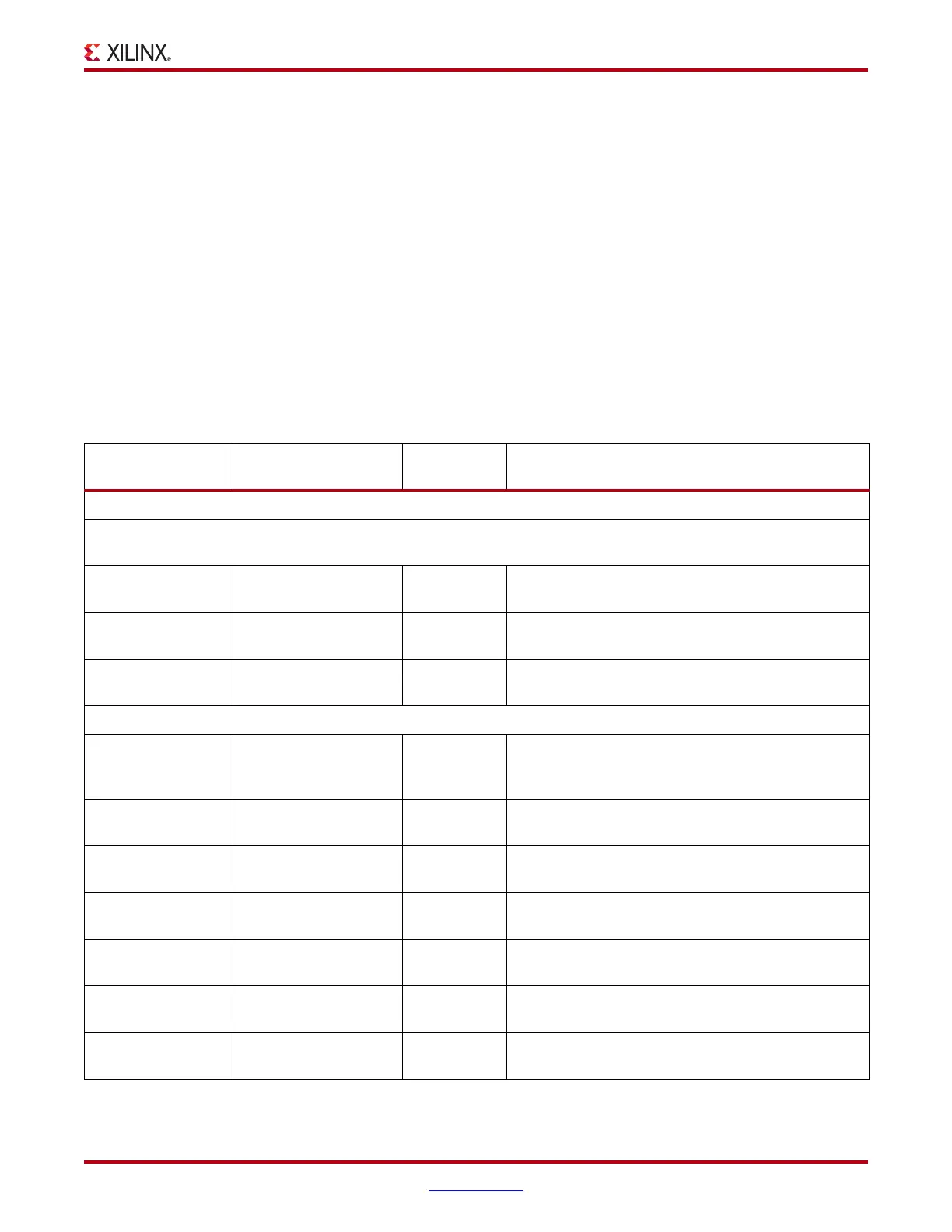

Table 4-20 shows the FIFO parameters.

Table 4-20: FIFO Timing Parameters

Parameter Function

Control

Signal

Description

Setup and Hold Relative to Clock (CLK)

T

RXCK

= Setup time (before clock edge)

T

RCKX

= Hold time (after clock edge)

T

RDCK_DI

/

T

RCKD_DI

(4)

Data inputs DI Time before/after WRCLK that D1 must be stable.

T

RCCK_RDEN

/

T

RCKC_RDEN

(5)

Read enable RDEN Time before/after RDCLK that RDEN must be stable.

T

RCCK_WREN

/

T

RCKC_WREN

(5)

Write enable WREN Time before/after WRCLK that WREN must be stable.

Clock to Out Delays

T

RCKO_DO

(1)

Clock to data output DO Time after RDCLK that the output data is stable at the

DO outputs of the FIFO. The synchronous FIFO with

DO_REG = 0 is different than in multirate mode.

T

RCKO_AEMPTY

(2)

Clock to almost empty

output

AEMPTY Time after RDCLK that the Almost Empty signal is

stable at the ALMOSTEMPTY outputs of the FIFO.

T

RCKO_AFULL

(2)

Clock to almost full

output

AFULL Time after WRCLK that the Almost Full signal is

stable at the ALMOSTFULL outputs of the FIFO.

T

RCKO_EMPTY

(2)

Clock to empty output EMPTY Time after RDCLK that the Empty signal is stable at

the EMPTY outputs of the FIFO.

T

RCKO_FULL

(2)

Clock to full output FULL Time after WRCLK that the Full signal is stable at the

FULL outputs of the FIFO.

T

RCKO_RDERR

(2)

Clock to read error

output

RDERR Time after RDCLK that the Read Error signal is stable

at the RDERR outputs of the FIFO.

T

RCKO_WRERR

(2)

Clock to write error

output

WRERR Time after WRCLK that the Write Error signal is stable

at the WRERR outputs of the FIFO.

Loading...

Loading...