Virtex-5 FPGA User Guide www.xilinx.com 155

UG190 (v5.0) June 19, 2009

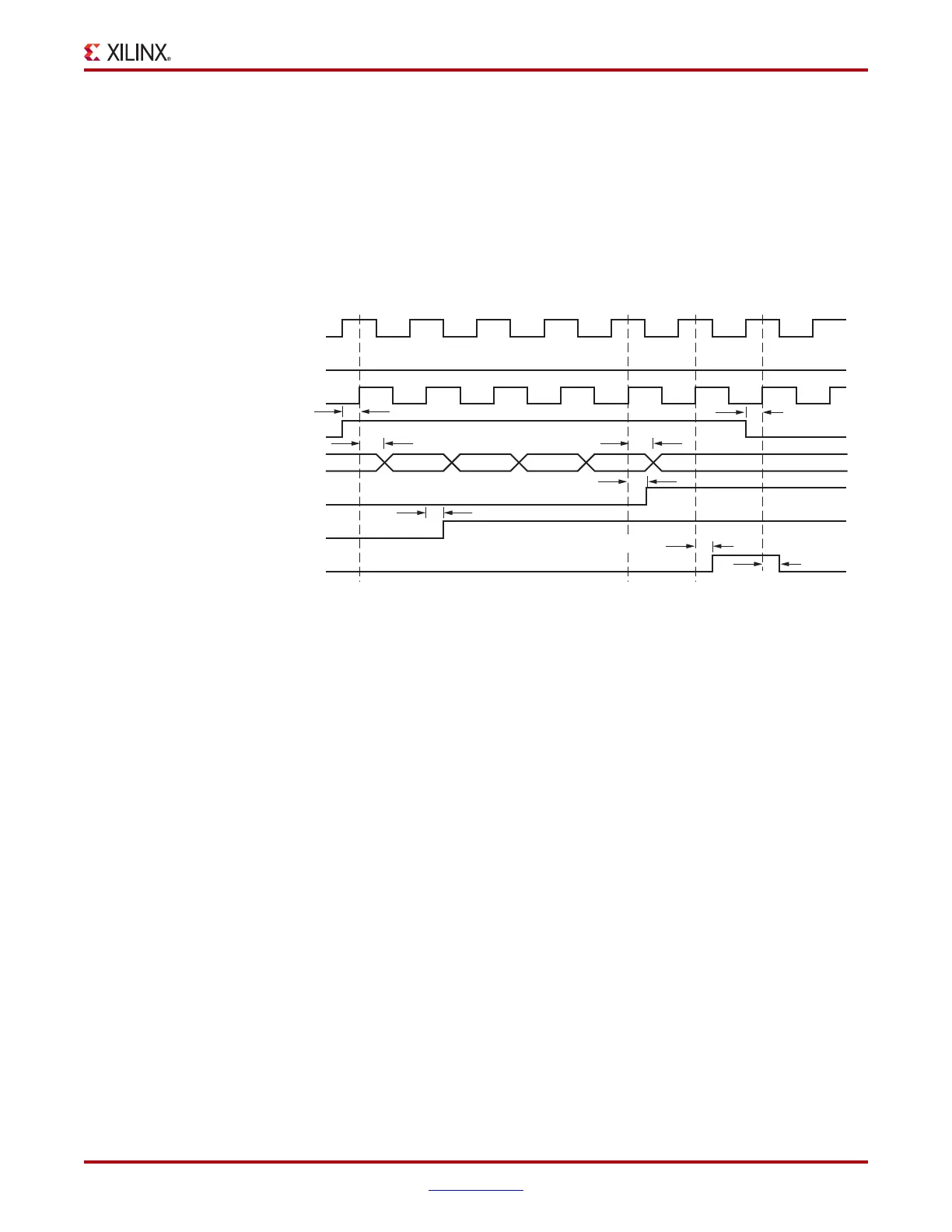

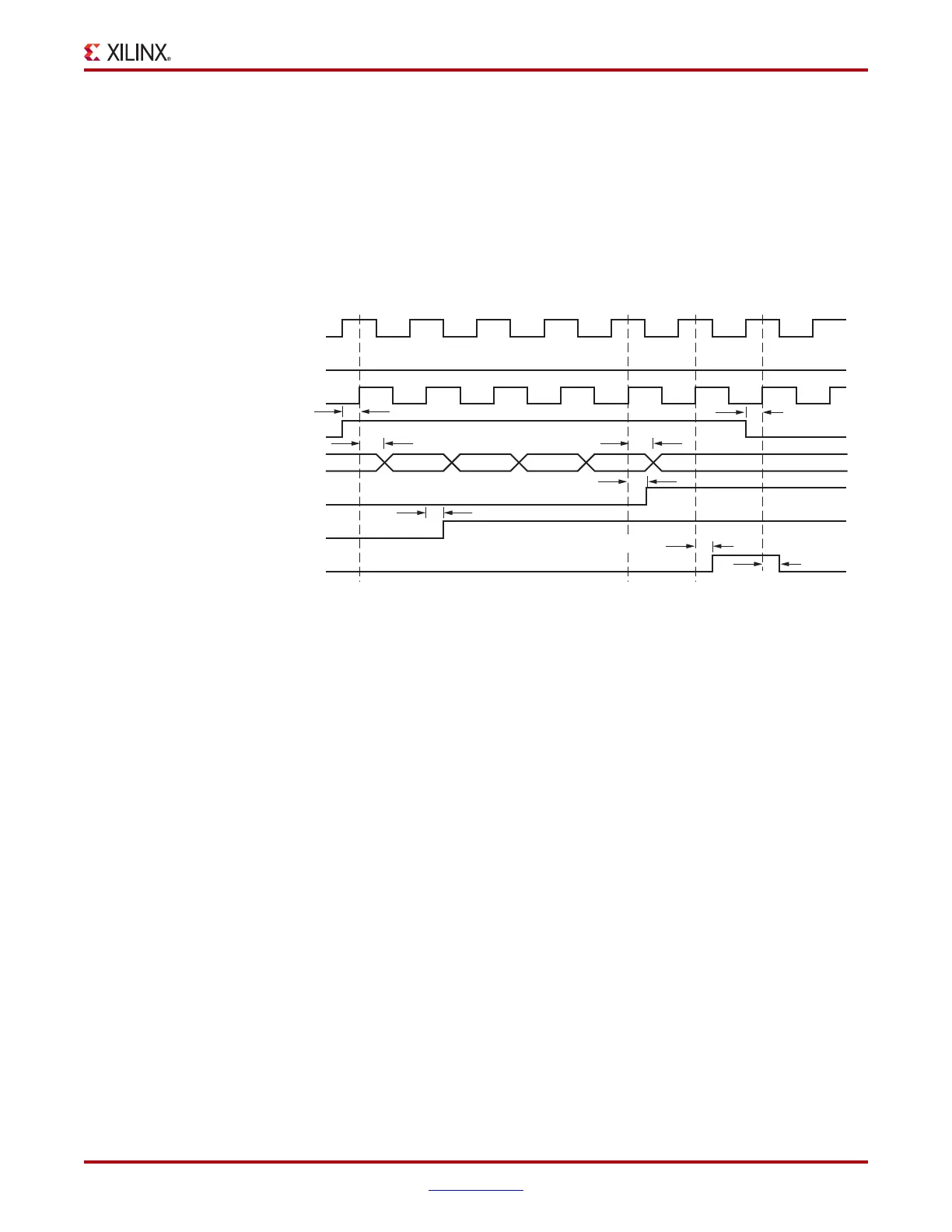

FIFO Timing Models and Parameters

There is minimum time between a rising read-clock and write-clock edge to guarantee that

AFULL will be deasserted. If this minimum is not met, the deassertion of AFULL can take

an additional write clock cycle.

Case 4: Reading From An Empty or Almost Empty FIFO

Prior to the operations performed in Figure 4-24, the FIFO is almost completely empty. In

this example, the timing diagram reflects standard mode. For FWFT mode, data at DO

appears one read-clock cycle earlier.

Clock Event 1: Read Operation and Assertion of Almost EMPTY Signal

During a read operation to an almost empty FIFO, the Almost EMPTY signal is asserted.

• At time T

FCCK_RDEN

, before clock event 1 (RDCLK), read enable becomes valid at the

RDEN input of the FIFO.

• At time T

FCKO_DO

, after clock event 1 (RDCLK), data 00 becomes valid at the DO

outputs of the FIFO.

• At time T

FCKO_AEMPTY

, one clock cycle after clock event 1 (RDCLK), Almost Empty is

asserted at the AEMPTY output pin of the FIFO.

Clock Event 2: Read Operation and Assertion of EMPTY Signal

The EMPTY signal pin is asserted when the FIFO is empty.

• Read enable remains asserted at the RDEN input of the FIFO.

• At time T

FCKO_DO

, after clock event 2 (RDCLK), data 04 (last data) becomes valid at

the DO outputs of the FIFO.

• At time T

FCKO_EMPTY

, after clock event 2 (RDCLK), Empty is asserted at the EMPTY

output pin of the FIFO.

In the event that the FIFO is empty and a write followed by a read is performed, the

EMPTY signal remains asserted.

X-Ref Target - Figure 4-24

Figure 4-24: Reading From an Empty / Almost Empty FIFO (Standard Mode)

ug190_4_21_032506

142

020100 03 04

3

WRCLK

WREN

RDCLK

RDEN

DO

EMPTY

AEMPTY

RDERR

T

FCCK_RDEN

T

FCKO_AEMPTY

T

FCKO_DO

T

FCKO_DO

T

FCKO_EMPTY

T

FCCK_RDEN

T

FCKO_RDERR

T

FCKO_RDERR

Loading...

Loading...