46 www.xilinx.com Virtex-5 FPGA User Guide

UG190 (v5.0) June 19, 2009

Chapter 1: Clock Resources

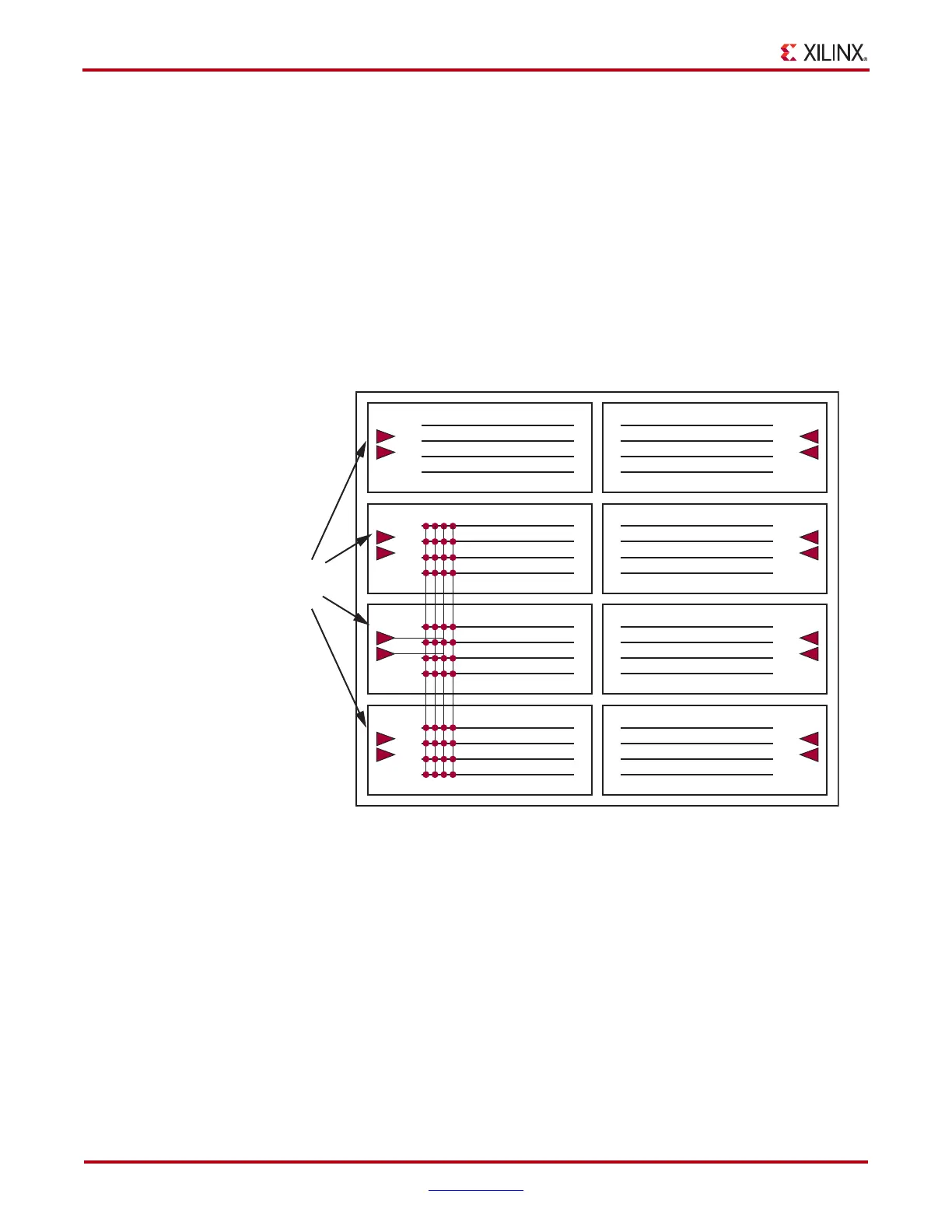

Regional Clock Nets

In addition to global clock trees and nets, Virtex-5 devices contain regional clock nets.

These clock trees are also designed for low-skew and low-power operation. Unused

branches are disconnected. The clock trees also manage the load/fanout when all the logic

resources are used.

Regional clock nets do not propagate throughout the whole Virtex-5 device. Instead, they

are limited to only one clock region. One clock region contains four independent regional

clock nets.

To access regional clock nets, BUFRs must be instantiated. A BUFR can drive regional

clocks in up to two adjacent clock regions (Figure 1-23). BUFRs in the top or bottom region

can only access one adjacent region; below or above respectively. The left side BUFRs can

feed the center column I/Os.

VHDL and Verilog Templates

The VHDL and Verilog code for all clocking resource primitives and ISE language

templates are available in the Libraries Guide.

X-Ref Target - Figure 1-23

Figure 1-23: BUFR Driving Multiple Regions

ug190_1_23_012306

BUFRs

Loading...

Loading...