Virtex-5 FPGA User Guide www.xilinx.com 43

UG190 (v5.0) June 19, 2009

Regional Clocking Resources

the global clock tree. Each BUFR can drive the four regional clock nets in the region it is

located, and the four clock nets in the adjacent clock regions (up to three clock regions).

Unlike BUFIOs, BUFRs can drive the I/O logic and logic resources (CLB, block RAM, etc.)

in the existing and adjacent clock regions. BUFRs can be driven by clock capable pins or

local interconnect. In addition, BUFR is capable of generating divided clock outputs with

respect to the clock input. The divide values are an integer between one and eight. BUFRs

are ideal for source-synchronous applications requiring clock domain crossing or serial-to-

parallel conversion. There are two BUFRs in a typical clock region (four regional clock

networks). The center column does not have BUFRs.

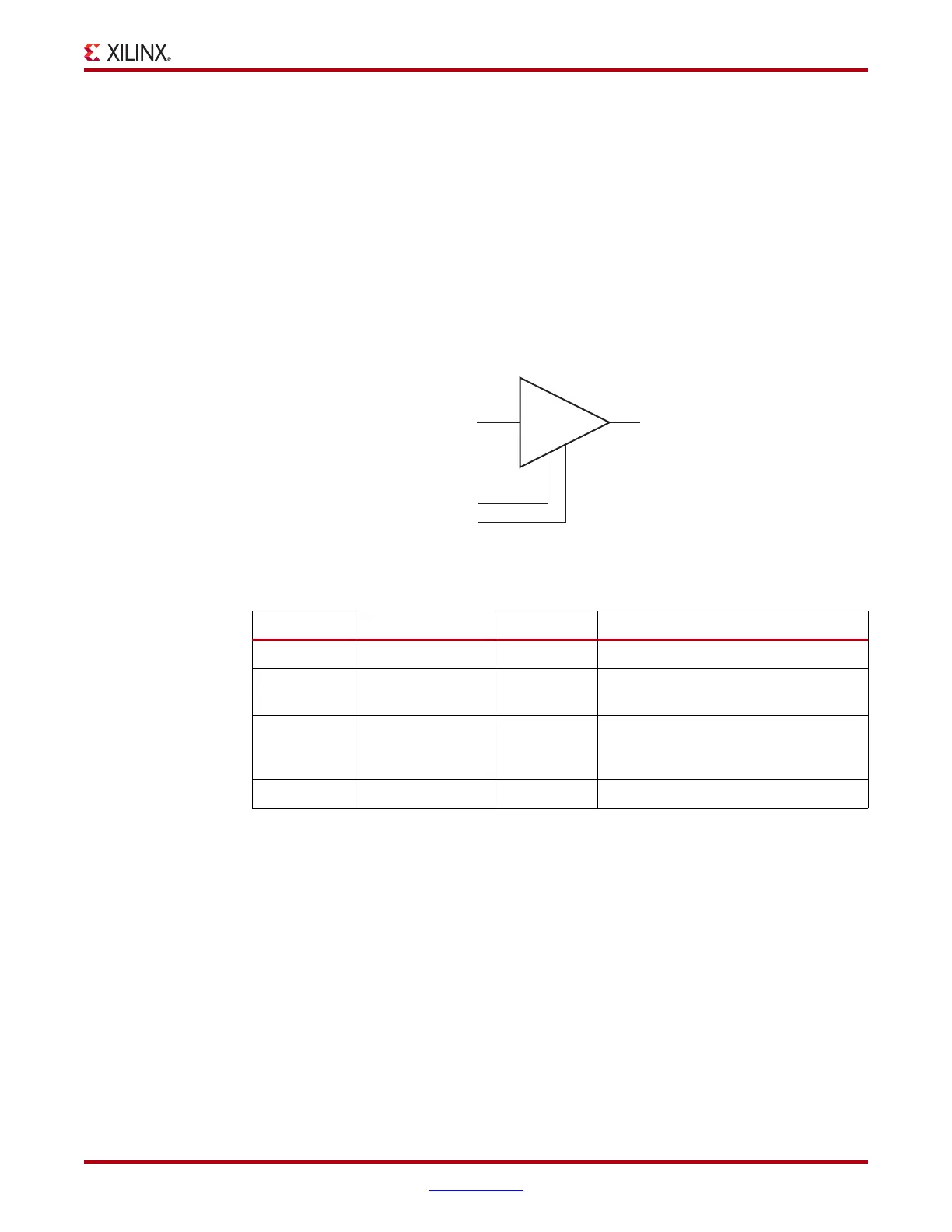

BUFR Primitive

BUFR is a clock-in/clock-out buffer with the capability to divide the input clock frequency.

Additional Notes on the CE Pin

When CE is asserted/deasserted, the output clock signal turns on/off. When global

set/reset (GSR) signal is High, BUFR does not toggle, even if CE is held High. The BUFR

output toggles after the GSR signal is deasserted when a clock is on the BUFR input port.

X-Ref Target - Figure 1-20

Figure 1-20: BUFR Primitive

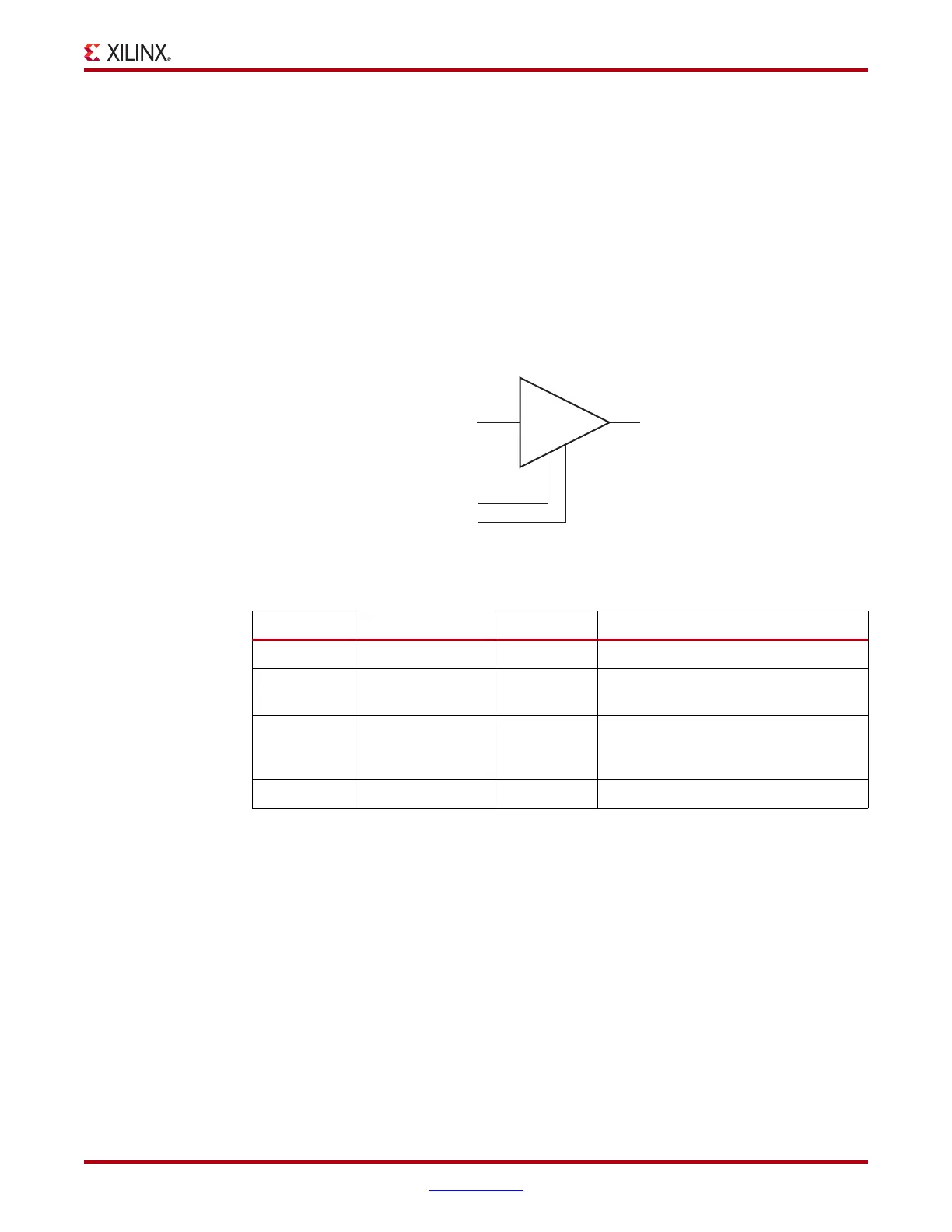

Table 1-7: BUFR Port List and Definitions

Port Name Type Width Definition

O Output 1 Clock output port

CE Input 1 Clock enable port. Cannot be used in

BYPASS mode.

CLR Input 1 Asynchronous clear for the divide

logic, and sets the output Low. Cannot

be used in BYPASS mode.

I Input 1 Clock input port

CLR

CE

IO

ug190_1_20_032306

Loading...

Loading...