92 www.xilinx.com Virtex-5 FPGA User Guide

UG190 (v5.0) June 19, 2009

Chapter 3: Phase-Locked Loops (PLLs)

General Usage Description

PLL Primitives

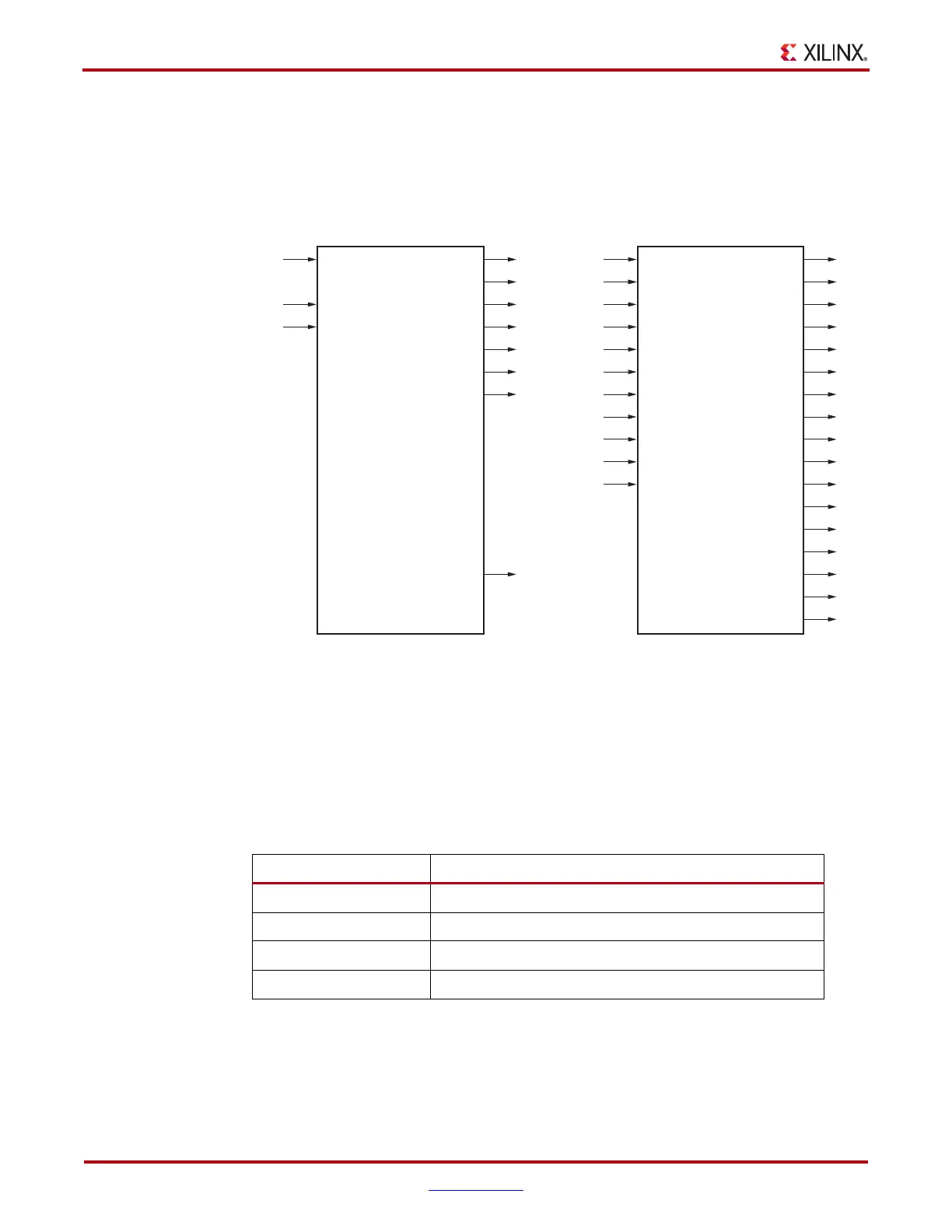

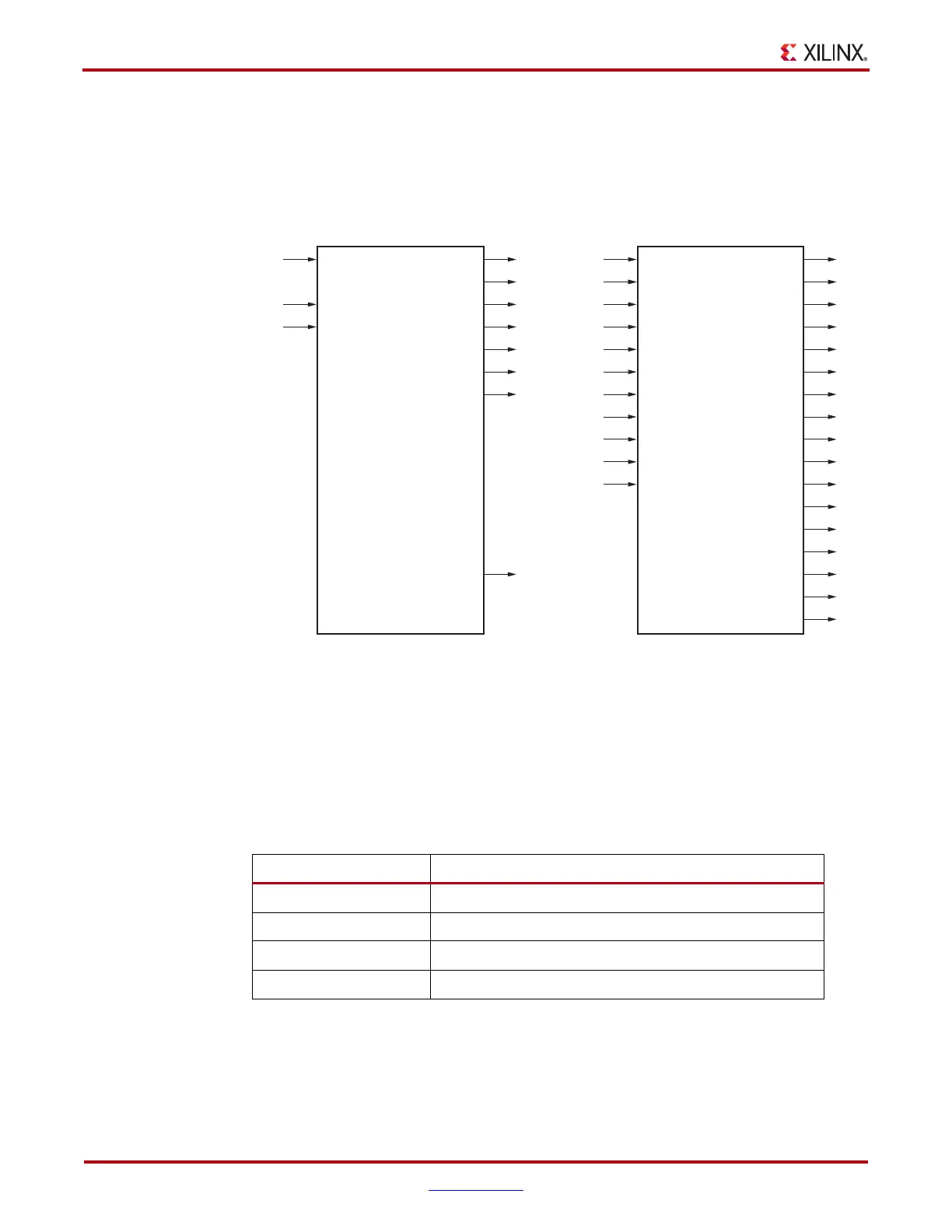

Figure 3-4 shows the two Virtex-5 FPGA PLL primitives, PLL_BASE and PLL_ADV.

PLL_BASE Primitive

The PLL_BASE primitive provides access to the most frequently used features of a stand

alone PLL. Clock deskew, frequency synthesis, coarse phase shifting, and duty cycle

programming are available to use with the PLL_BASE. The ports are listed in Table 3-1.

X-Ref Target - Figure 3-4

Figure 3-4: PLL Primitives

CLKIN1

CLKFBIN

RST

CLKOUT0

CLKOUT1

CLKOUT2

CLKOUT3

CLKOUT4

CLKOUT5

CLKFBOUT

LOCKED

PLL_BASE

UG190_c3_04_022709

CLKIN1

CLKIN2

CLKFBIN

CLKINSEL

DADDR[4:0]

DI[15:0]

DWE

DEN

DCLK

REL

RST

CLKOUT0

CLKOUT1

CLKOUT2

CLKOUT3

CLKOUT4

CLKOUT5

CLKFBOUT

CLKOUTDCM0

CLKOUTDCM1

CLKOUTDCM2

CLKOUTDCM3

CLKOUTDCM4

CLKOUTDCM5

CLKFBDCM

LOCKED

DO[15:0]

DRDY

PLL_ADV

Table 3-1: PLL_BASE Ports

Description Port

Clock Input CLKIN, CLKFBIN

Control Inputs RST

Clock Output CLKOUT0 to CLKOUT5, CLKFBOUT

Status and Data Outputs LOCKED

Loading...

Loading...