Virtex-5 FPGA User Guide www.xilinx.com 177

UG190 (v5.0) June 19, 2009

CLB Overview

CLB/Slice Configurations

Table 5-1 summarizes the logic resources in one CLB. Each CLB or slice can be

implemented in one of the configurations listed. Table 5-2 shows the available resources in

all CLBs.

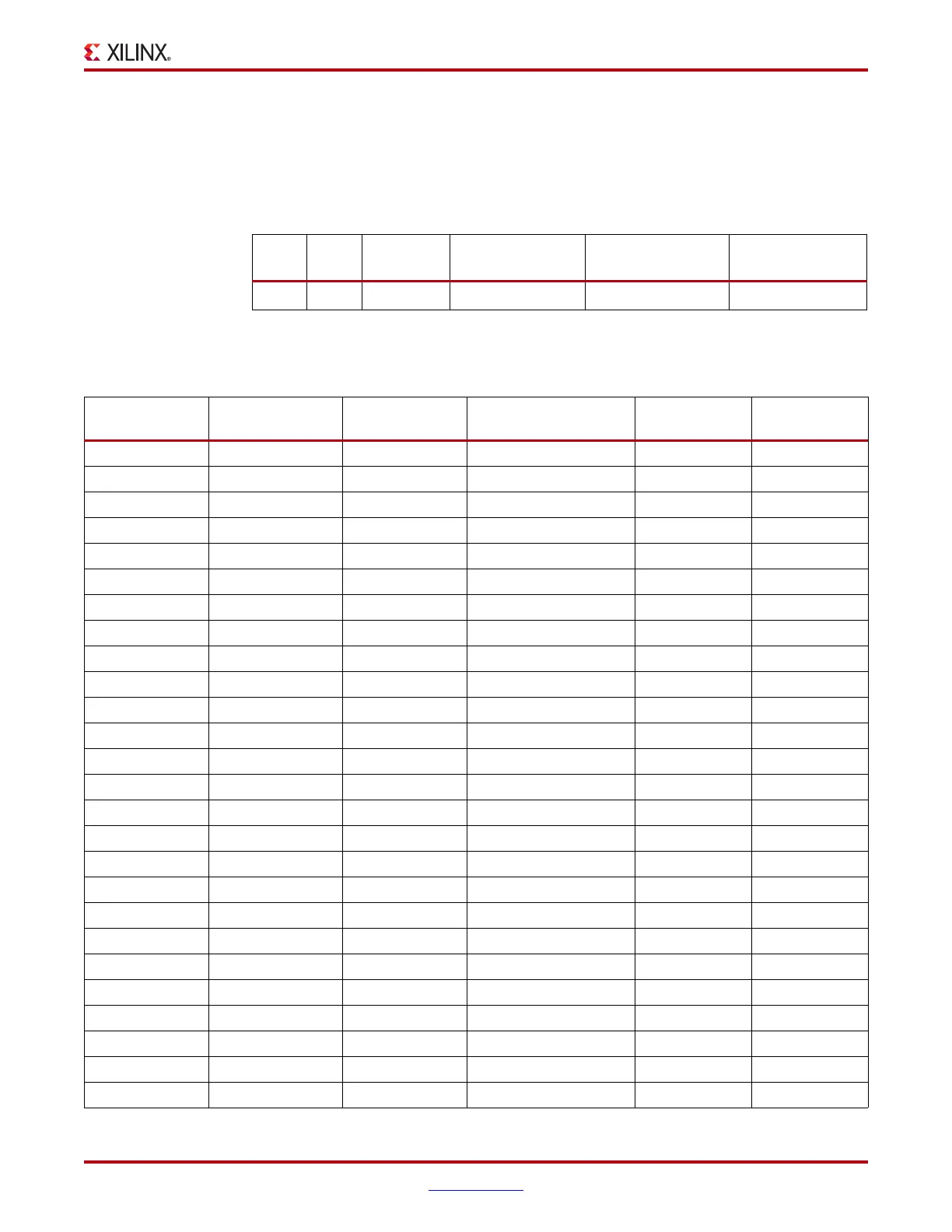

Table 5-1: Logic Resources in One CLB

Slices LUTs Flip-Flops

Arithmetic and

Carry Chains

Distributed RAM

(1)

Shift Registers

(1)

2 8 8 2 256 bits 128 bits

Notes:

1. SLICEM only, SLICEL does not have distributed RAM or shift registers.

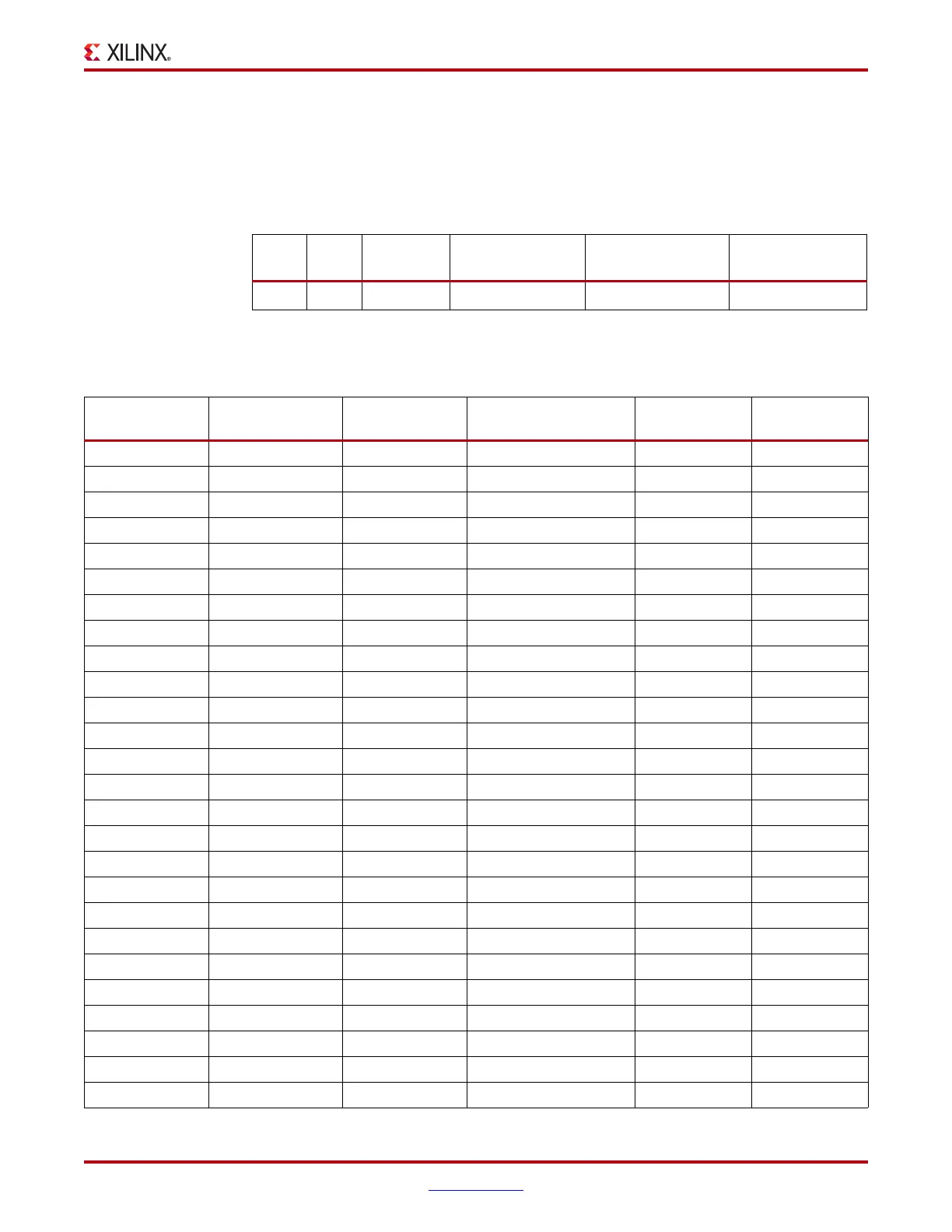

Table 5-2: Virtex-5 FPGA Logic Resources Available in All CLBs

Device

CLB Array

Row x Column

Number of

6-Input LUTs

Maximum

Distributed RAM (Kb)

Shift

Register (Kb)

Number of

Flip-Flops

XC5VLX20T 60 x 26 12,480 210 105 12,480

XC5VLX30 80 x 30 19,200 320 160 19,200

XC5VFX30T 80 x 38 20,480 380 190 20,480

XC5VLX30T 80 x 30 19,200 320 160 19,200

XC5VSX35T 80 x 34 21,760 520 260 21,760

XC5VLX50 120 x 30 28,800 480 240 28,800

XC5VLX50T 120 x 30 28,800 480 240 28,800

XC5VSX50T 120 x 34 32,640 780 390 32,640

XC5VFX70T 160 x 38 44,800 820 410 44,800

XC5VLX85 120 x 54 51,840 840 420 51,840

XC5VLX85T 120 x 54 51,840 840 420 51,840

XC5VSX95T 160 x 46 58,880 1,520 760 58,880

XC5VFX100T 160 x 56 64,000 1,240 620 64,000

XC5VLX110 160 x 54 69,120 1,120 560 69,120

XC5VLX110T 160 x 54 69,120 1,120 560 69,120

XC5VFX130T 200 x 56 81,920 1,580 790 81,920

XC5VTX150T 200 x 58 92,800 1,500 750 92,800

XC5VLX155 160 x 76 97,280 1,640 820 97,280

XC5VLX155T 160 x 76 97,280 1,640 820 97,280

XC5VFX200T 240 x 68 122,880 2,280 1140 122,880

XC5VLX220 160 x 108 138,240 2,280 1140 138,240

XC5VLX220T 160 x 108 138,240 2,280 1140 138,240

XC5VSX240T 240 x 78 149,760 4,200 2100 149,760

XC5VTX240T 240 x 78 149,760 2,400 1200 149,760

XC5VLX330 240 x 108 207,360 3,420 1710 207,360

XC5VLX330T 240 x 108 207,360 3,420 1710 207,360

Loading...

Loading...