332 www.xilinx.com Virtex-5 FPGA User Guide

UG190 (v5.0) June 19, 2009

Chapter 7: SelectIO Logic Resources

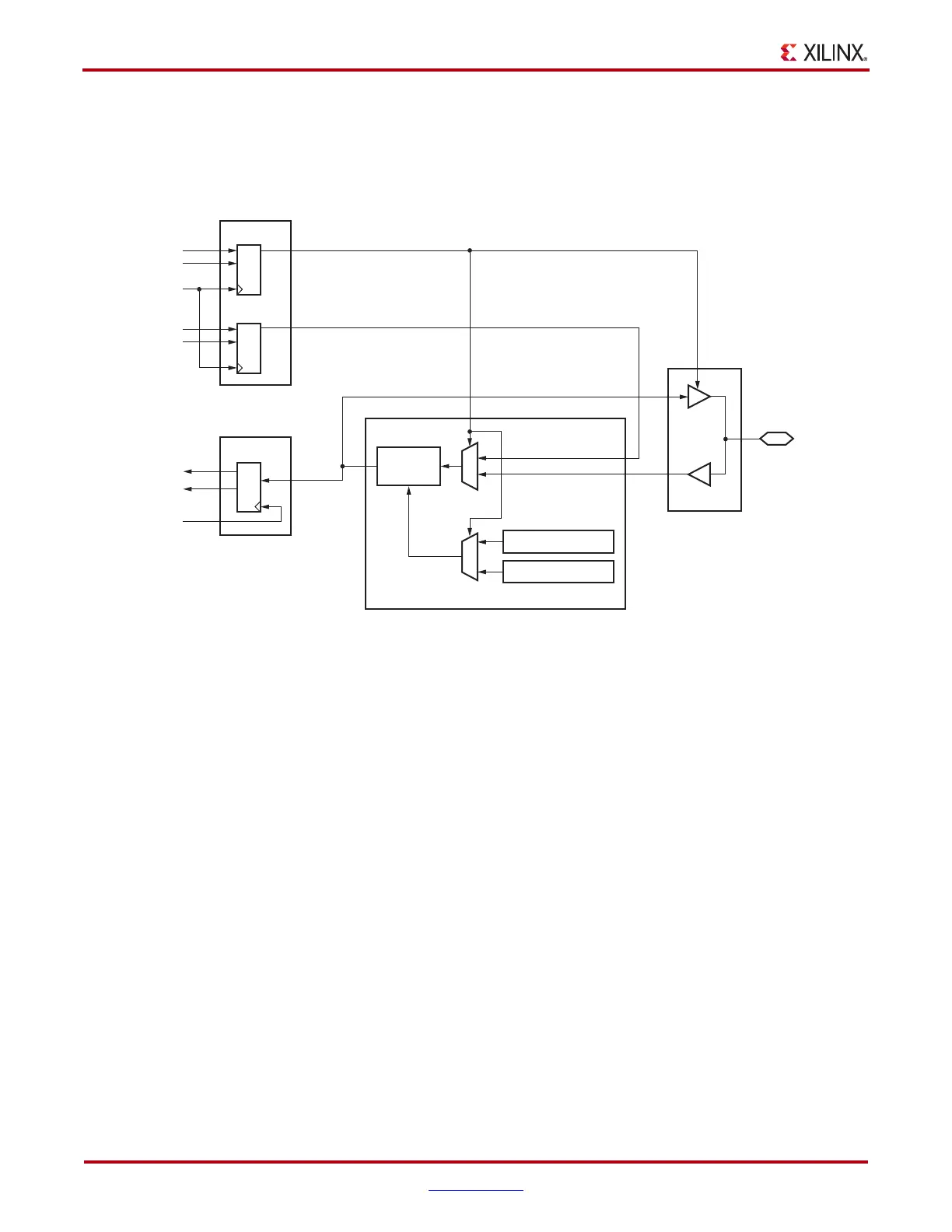

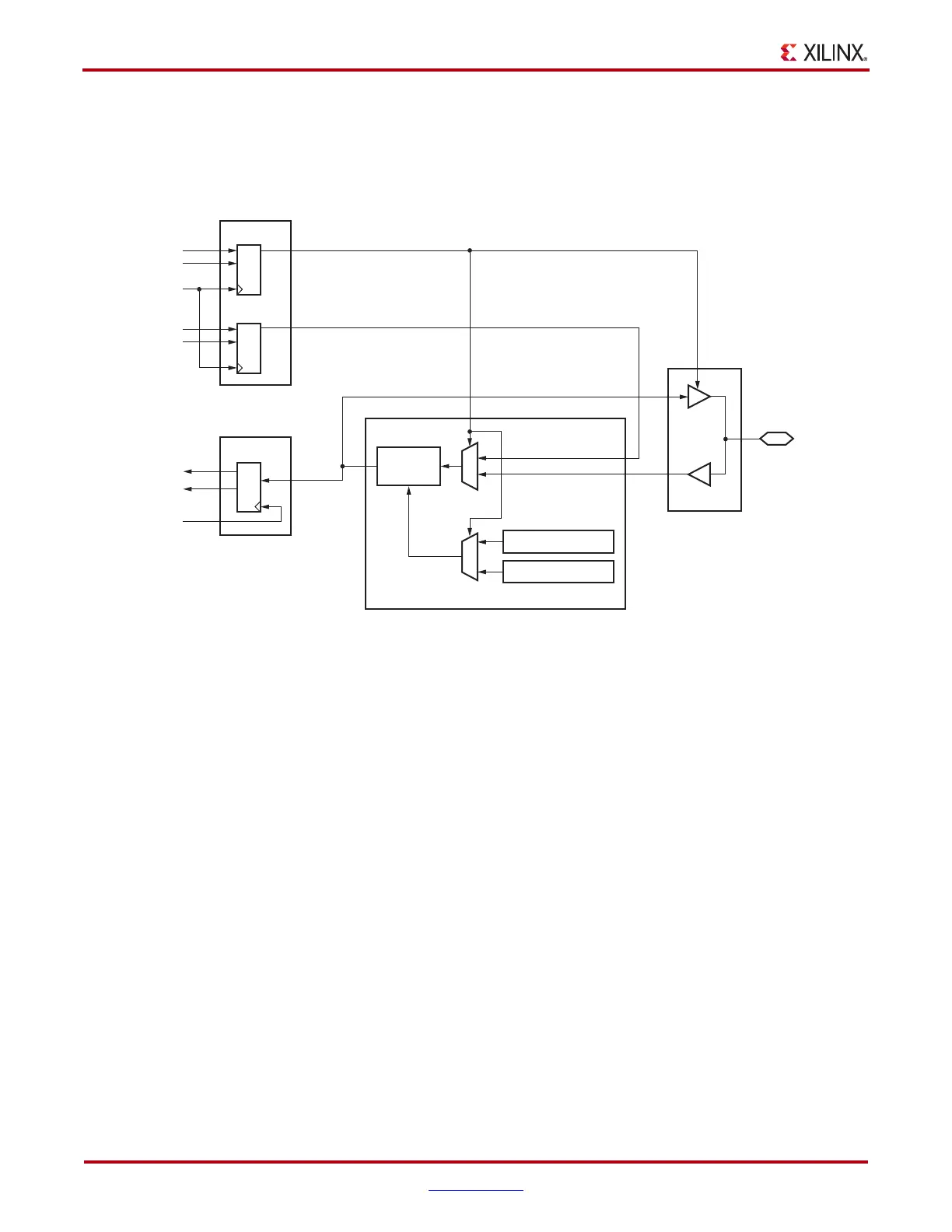

IODELAY Turnaround Time Usage Model

When using IODELAY in bidirectional mode, the turnaround time needs to be considered.

Figure 7-10 shows a simplified block diagram of the IODELAY in the Virtex-5 FPGA IOB

that applies to one use of the bidirectional IODELAY functionality.

When DELAY_SRC = IO, MUXE and MUXF dynamically selects ODATAIN or IDATAIN

and ODELAY_VALUE or IDELAY_VALUE inside the IODELAY block.

The following Verilog code segment is used for demonstrating bidirectional IODELAY:

IDDR #(

.DDR_CLK_EDGE ("SAME_EDGE"),

.INIT_Q1 (1'b0),

.INIT_Q2 (1'b0),

.SRTYPE ("SYNC")

)IDDR_INST (

.C(clk),

.CE(1'b1),

.D(DATAOUT),

.R(1'b0),

.S(1'b0),

.Q1(Q1),

.Q2(Q2)

);

IOBUF #(

.IOSTANDARD ("LVCMOS25")

)IOBUF_INST (

.I(DATAOUT),

.T(TSCONTROL),

.O(IDATAIN),

.IO(IOPAD_DATA)

);

X-Ref Target - Figure 7-10

Figure 7-10: Basic Sections of Blocks Related to IODELAY Turnaround with Pertinent Paths Shown

IODELAY_01_081407

IOB

IODELAY

T

Q1

Q2

T2

CLK

CLK

MUX E

Delay

Chain

ODATAIN

IDATAIN

MUX F

OBUF

PA D

IBUF

D1

T1

D2

ODELAY_VALUE

IDELAY_VALUE

ODDR

TSCONTROL

ODATAIN

DATAOUT

ODDR

IDDR

Loading...

Loading...