118 www.xilinx.com Virtex-5 FPGA User Guide

UG190 (v5.0) June 19, 2009

Chapter 4: Block RAM

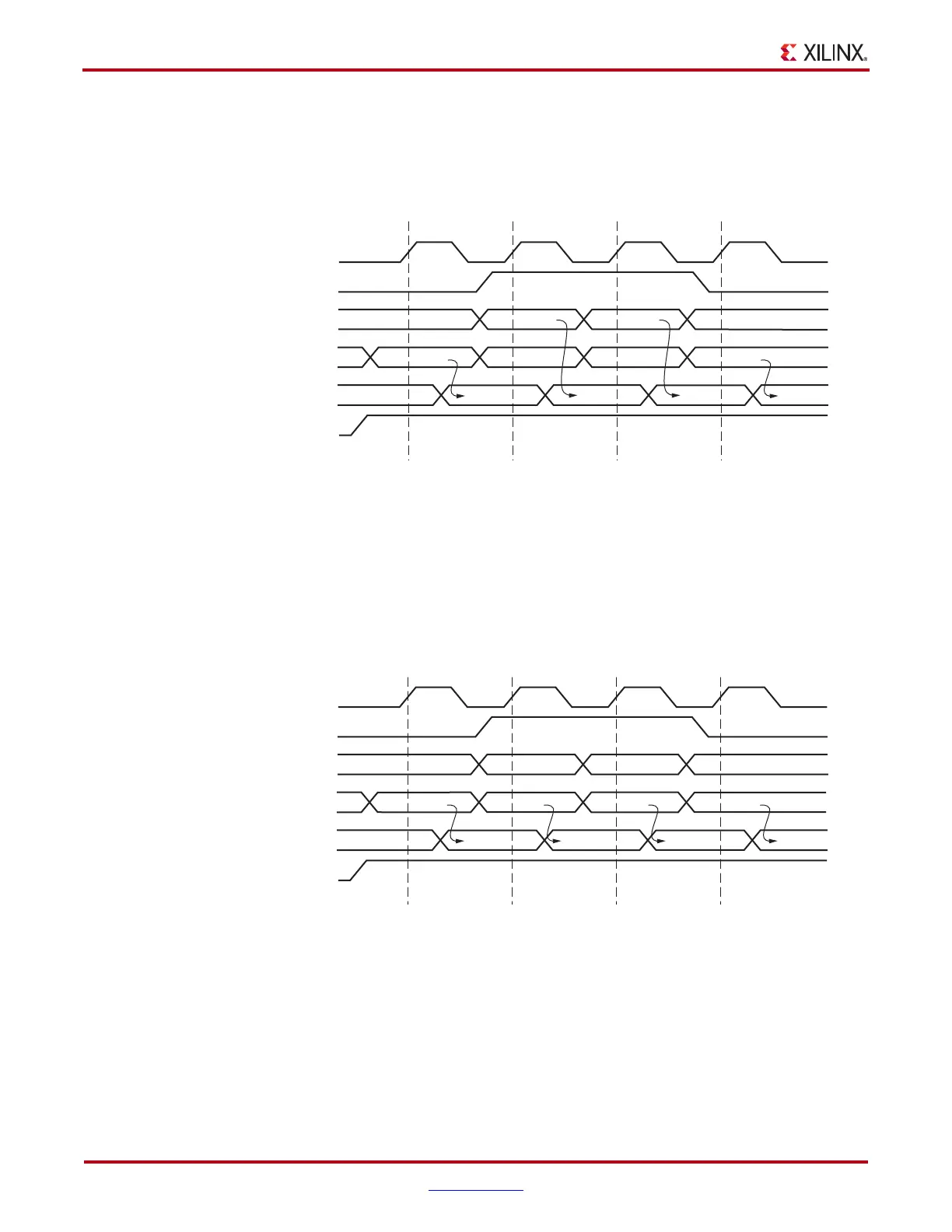

WRITE_FIRST or Transparent Mode (Default)

In WRITE_FIRST mode, the input data is simultaneously written into memory and stored

in the data output (transparent write), as shown in Figure 4-2. These waveforms

correspond to latch mode when the optional output pipeline register is not used.

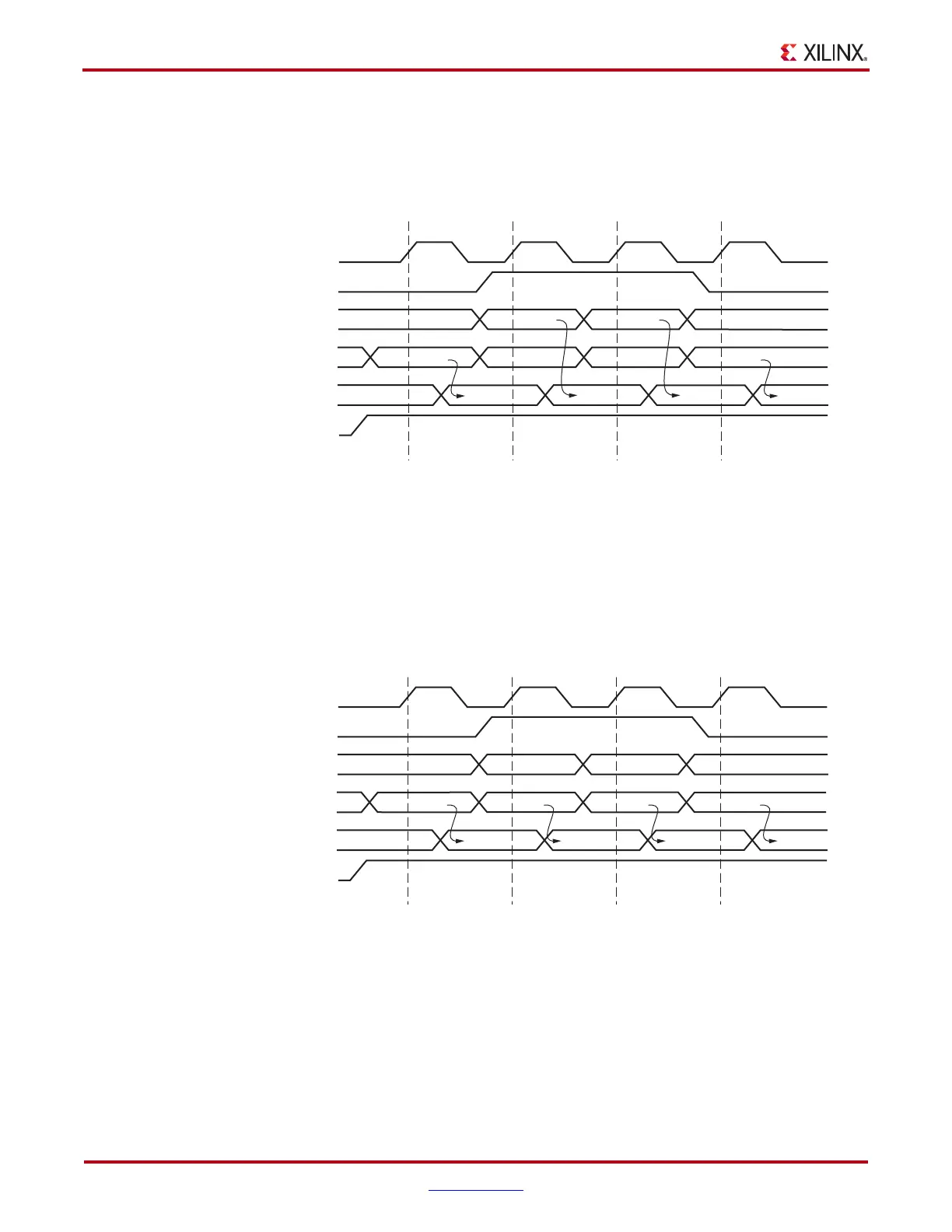

READ_FIRST or Read-Before-Write Mode

In READ_FIRST mode, data previously stored at the write address appears on the output

latches, while the input data is being stored in memory (read before write). The waveforms

in Figure 4-3 correspond to latch mode when the optional output pipeline register is not

used.

NO_CHANGE Mode

In NO_CHANGE mode, the output latches remain unchanged during a write operation.

As shown in Figure 4-4, data output remains the last read data and is unaffected by a write

operation on the same port. These waveforms correspond to latch mode when the optional

output pipeline register is not used.

X-Ref Target - Figure 4-2

Figure 4-2: WRITE_FIRST Mode Waveforms

CLK

WE

DI

ADDR

DO

EN

Disabled Read

XXXX 1111 2222 XXXX

aa bb cc dd

0000 MEM(aa) 1111 2222 MEM(dd)

ReadWrite

MEM(bb)=1111

Write

MEM(cc)=2222

ug190_4_03_032206

X-Ref Target - Figure 4-3

Figure 4-3: READ_FIRST Mode Waveforms

CLK

WE

DI

ADDR

DO

EN

Disabled Read

XXXX 1111 2222 XXXX

aa bb cc dd

0000 MEM(aa) old MEM(bb) old MEM(cc) MEM(dd)

ReadWrite

MEM(bb)=1111

Write

MEM(cc)=2222

ug190_4_04_032206

Loading...

Loading...