44 www.xilinx.com Virtex-5 FPGA User Guide

UG190 (v5.0) June 19, 2009

Chapter 1: Clock Resources

BUFR Attributes and Modes

Clock division in the BUFR is controlled in software through the BUFR_DIVIDE attribute.

Table 1-8 lists the possible values when using the BUFR_DIVIDE attribute.

The propagation delay through BUFR is different for BUFR_DIVIDE = 1 and

BUFR_DIVIDE = BYPASS. When set to 1, the delay is slightly more than BYPASS. All other

divisors have the same delay BUFR_DIVIDE = 1. The phase relationship between the input

clock and the output clock is the same for all possible divisions except BYPASS.

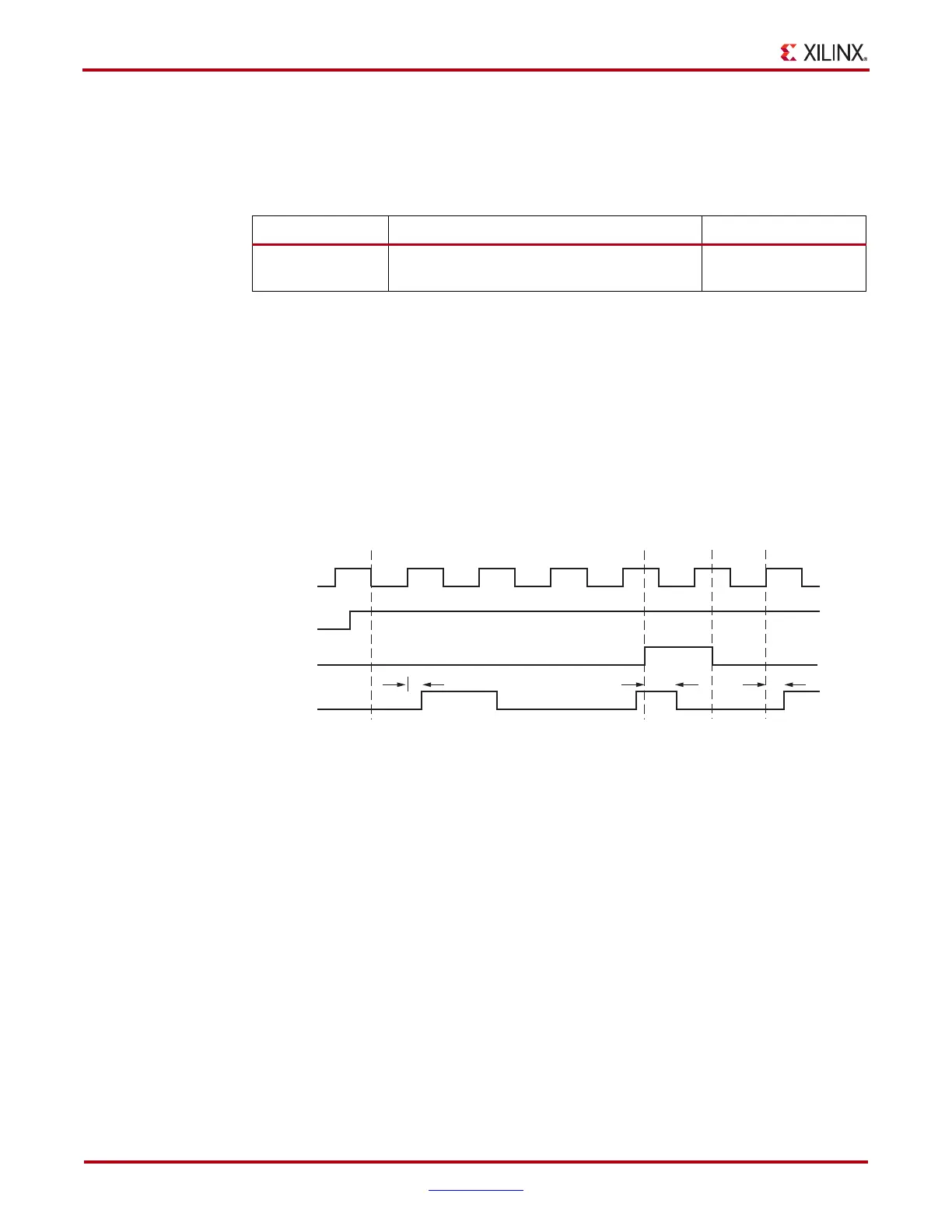

The timing relationship between the inputs and output of BUFR when using the

BUFR_DIVIDE attribute is illustrated in Figure 1-21. In this example, the BUFR_DIVIDE

attribute is set to three. Sometime before this diagram CLR was asserted.

In Figure 1-21:

• Before clock event 1, CE is asserted High.

• After CE is asserted and time T

BRCKO_O

, the output O begins toggling at the divide by

three rate of the input I. T

BRCKO_O

and other timing numbers are best found in the

speed specification.

Note: The duty cycle is not 50/50 for odd division. The Low pulse is one cycle of I

longer.

• At time event 2, CLR is asserted. After T

BRDO_CLRO

from time event 2, O stops

toggling.

• At time event 3, CLR is deasserted.

• At time T

BRCKO_O

after clock event 4, O begins toggling again at the divided by three

rate of I.

Table 1-8: BUFR_DIVIDE Attribute

Attribute Name Description Possible Values

BUFR_DIVIDE Defines whether the output clock is a divided

version of the input clock.

1, 2, 3, 4, 5, 6, 7, 8

BYPASS (default)

Notes:

1. Location constraint is available for BUFR.

X-Ref Target - Figure 1-21

Figure 1-21: BUFR Timing Diagrams with BUFR_DIVIDE Values

ug190_1_21_041808

T

BRCKO_O

T

BRCKO_O

T

BRDO_CLRO

I

CE

CLR

O

1234

Loading...

Loading...