218 www.xilinx.com Virtex-5 FPGA User Guide

UG190 (v5.0) June 19, 2009

Chapter 6: SelectIO Resources

SelectIO Resources Introduction

All Virtex-5 FPGAs have configurable high-performance SelectIO™ drivers and receivers,

supporting a wide variety of standard interfaces. The robust feature set includes

programmable control of output strength and slew rate, and on-chip termination using

Digitally Controlled Impedance (DCI).

Each IOB contains both input, output, and 3-state SelectIO drivers. These drivers can be

configured to various I/O standards. Differential I/O uses the two IOBs grouped together

in one tile.

• Single-ended I/O standards (LVCMOS, LVTTL, HSTL, SSTL, GTL, PCI)

• Differential I/O standards (LVDS, HT, LVPECL, BLVDS, Differential HSTL and SSTL)

• Differential and V

REF

dependent inputs are powered by V

CCAUX

Each Virtex-5 FPGA I/O tile contains two IOBs, and also two ILOGIC blocks and two

OLOGIC blocks, as described in Chapter 7, “SelectIO Logic Resources.”

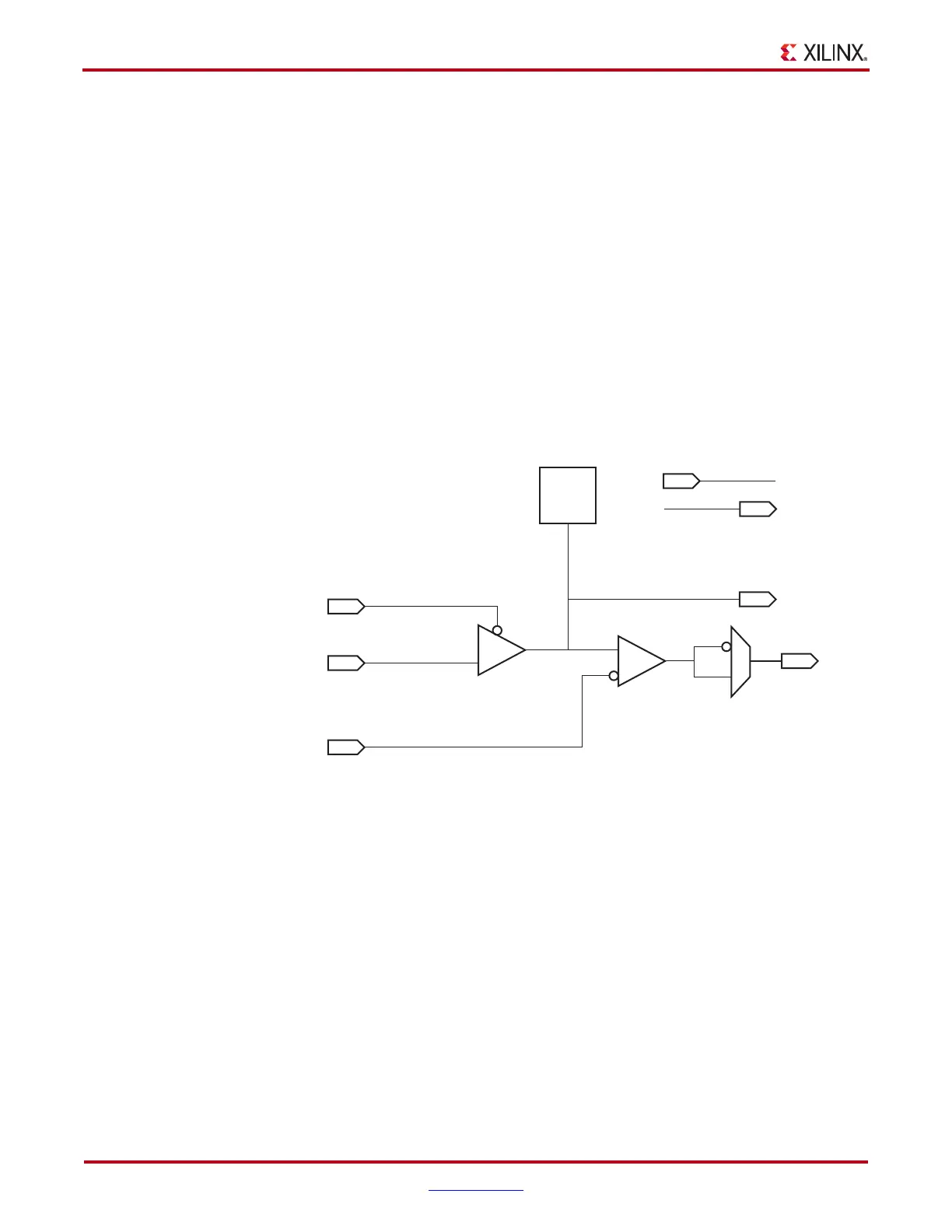

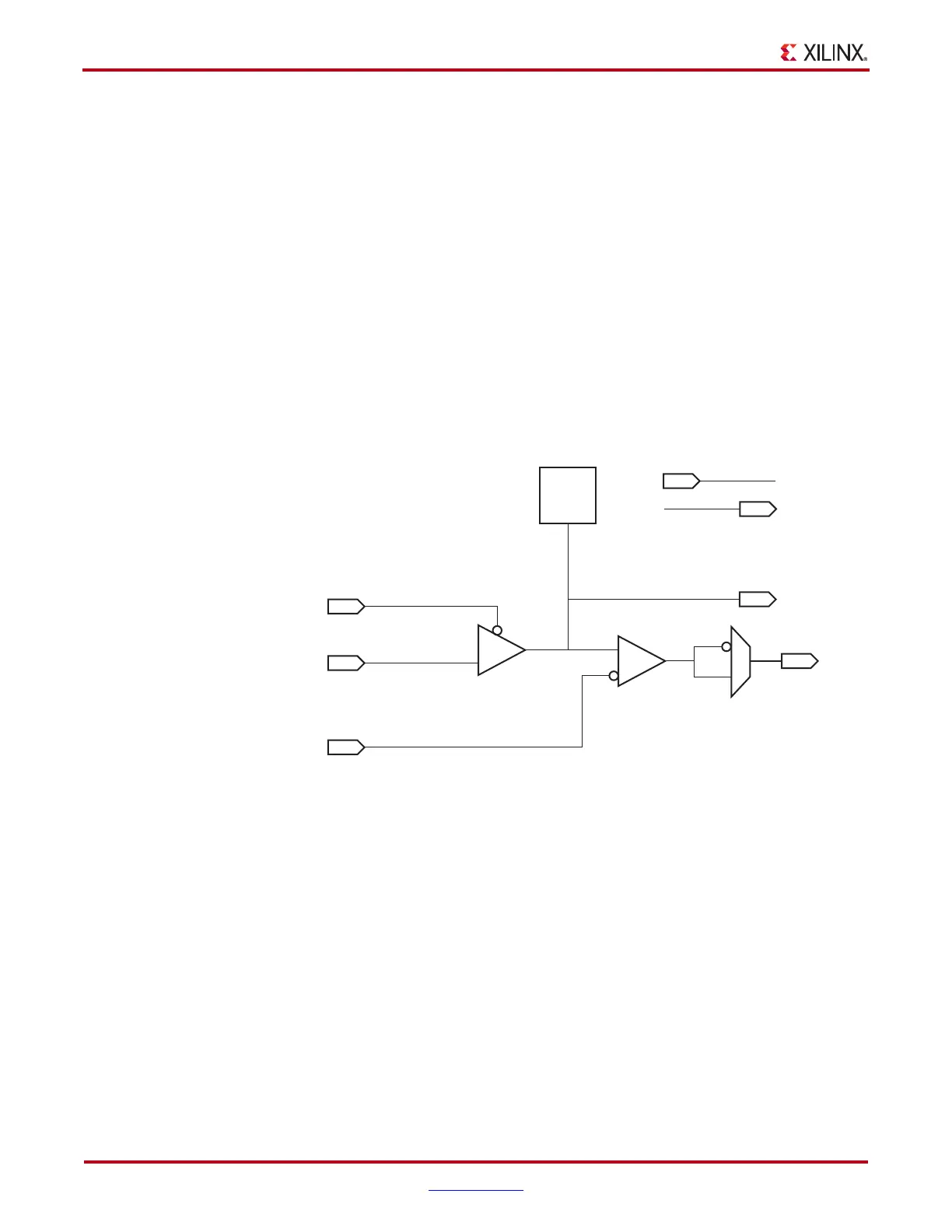

Figure 6-2 shows the basic IOB and its connections to the internal logic and the device Pad.

Each IOB has a direct connection to an ILOGIC/OLOGIC pair containing the input and

output logic resources for data and 3-state control for the IOB. Both ILOGIC and OLOGIC

can be configured as ISERDES and OSERDES, respectively, as described in Chapter 8,

“Advanced SelectIO Logic Resources.”

SelectIO Resources General Guidelines

This section summarizes the general guidelines to be considered when designing with the

SelectIO resources in Virtex-5 FPGAs.

Virtex-5 FPGA I/O Bank Rules

In Virtex-5 devices, with some exceptions in the center column, an I/O bank consists of 40

IOBs (20 CLBs high and a single clock region). There are always four half-sized banks

(20 IOBs) and a single configuration bank in the center column. The number of banks

X-Ref Target - Figure 6-2

Figure 6-2: Basic IOB Diagram

ug190_6_02_021306

PADOUT

DIFFO_IN

DIFFO_OUT

I

T

O

DIFFI_IN

OUTBUF

INBUF

PA D

Loading...

Loading...