28 www.xilinx.com Virtex-5 FPGA User Guide

UG190 (v5.0) June 19, 2009

Chapter 1: Clock Resources

Global Clock Buffer Primitives

The primitives in Table 1-2 are different configurations of the global clock buffers.

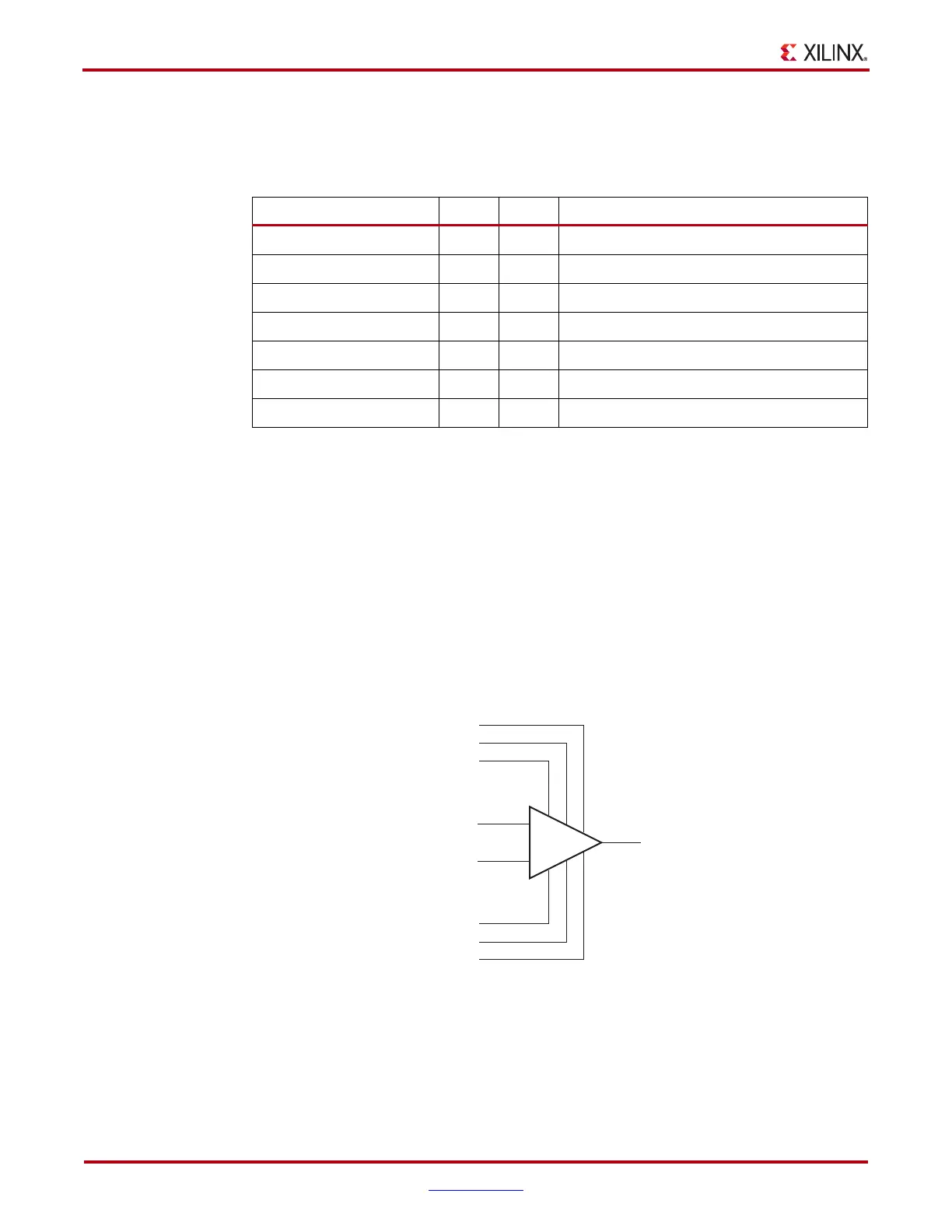

BUFGCTRL

The BUFGCTRL primitive shown in Figure 1-1, can switch between two asynchronous

clocks. All other global clock buffer primitives are derived from certain configurations of

BUFGCTRL. The ISE® software tools manage the configuration of all these primitives.

BUFGCTRL has four select lines, S0, S1, CE0, and CE1. It also has two additional control

lines, IGNORE0 and IGNORE1. These six control lines are used to control the input I0 and

I1.

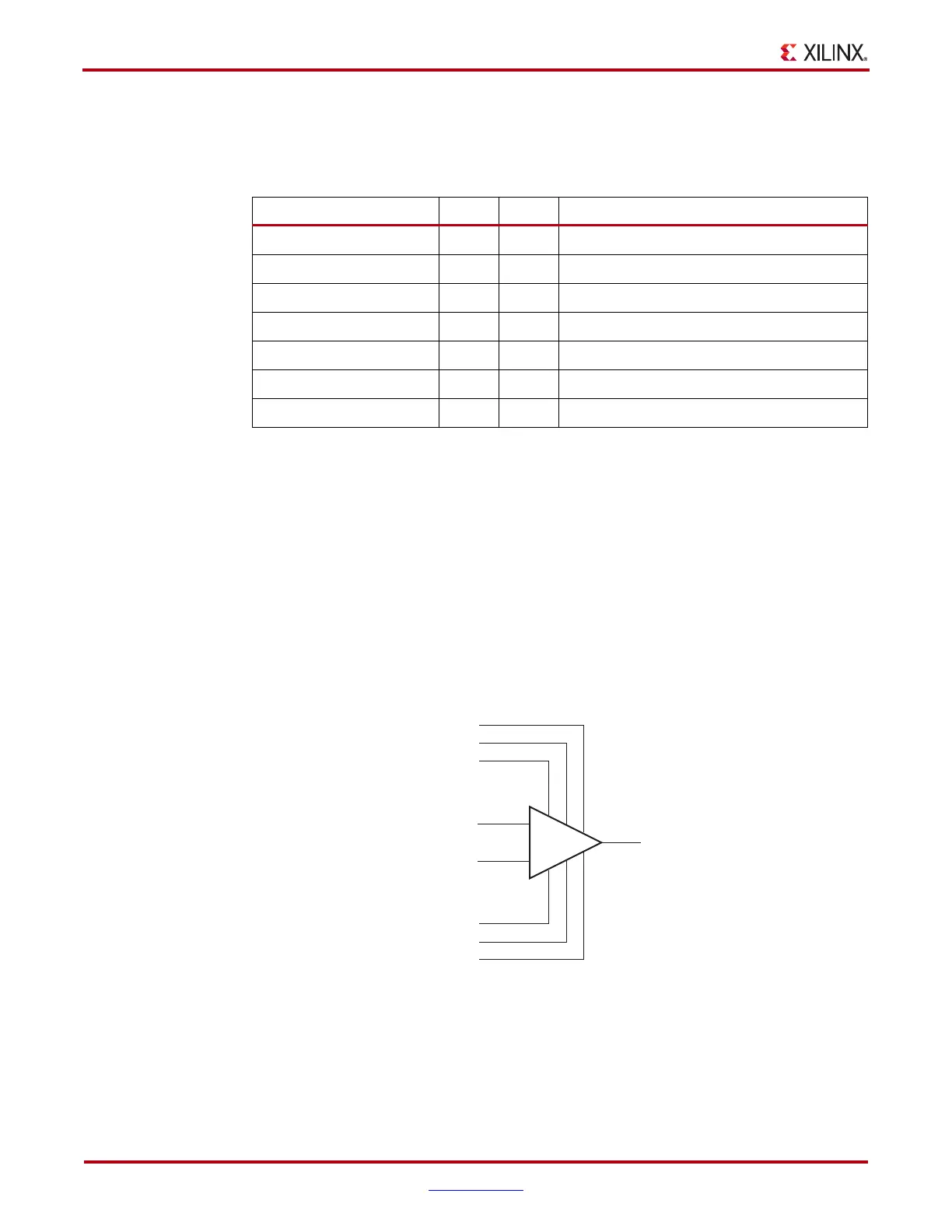

Table 1-2: Global Clock Buffer Primitives

Primitive

(1)

Input Output Control

BUFGCTRL I0, I1 O CE0, CE1, IGNORE0, IGNORE1, S0, S1

BUFG I O –

BUFGCE I O CE

BUFGCE_1 I O CE

BUFGMUX I0, I1 O S

BUFGMUX_1 I0, I1 O S

BUFGMUX_CTRL

(2)

I0, I1 O S

Notes:

1. All primitives are derived from a software preset of BUFGCTRL.

2. This primitive replaces the BUFGMUX_VIRTEX4 primitive.

X-Ref Target - Figure 1-1

Figure 1-1: BUFGCTRL Primitive

IGNORE1

IGNORE0

CE1

CE0

S1

S0

I1

I0

O

BUFGCTRL

ug190_1_01_032206

Loading...

Loading...