Virtex-5 FPGA User Guide www.xilinx.com 161

UG190 (v5.0) June 19, 2009

Built-in Error Correction

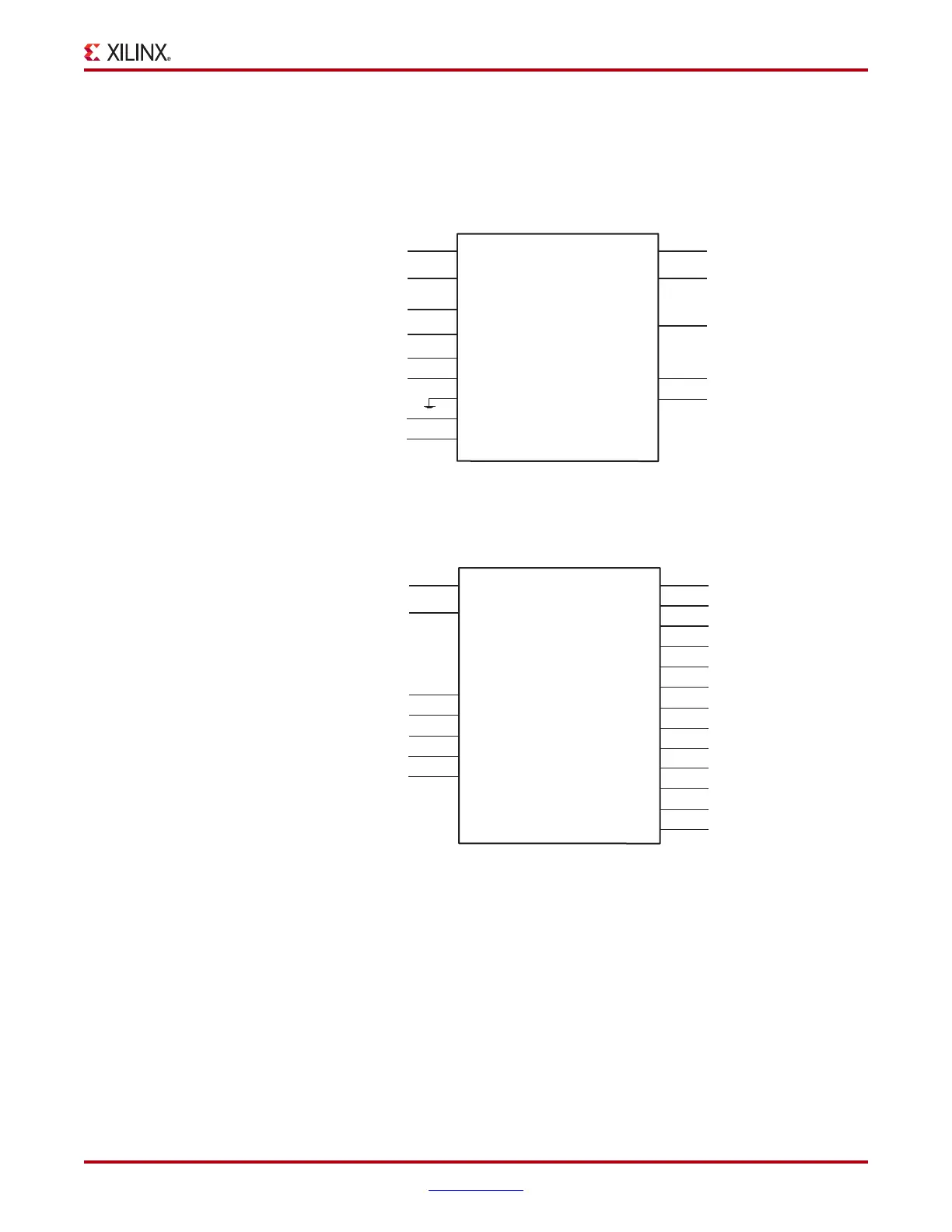

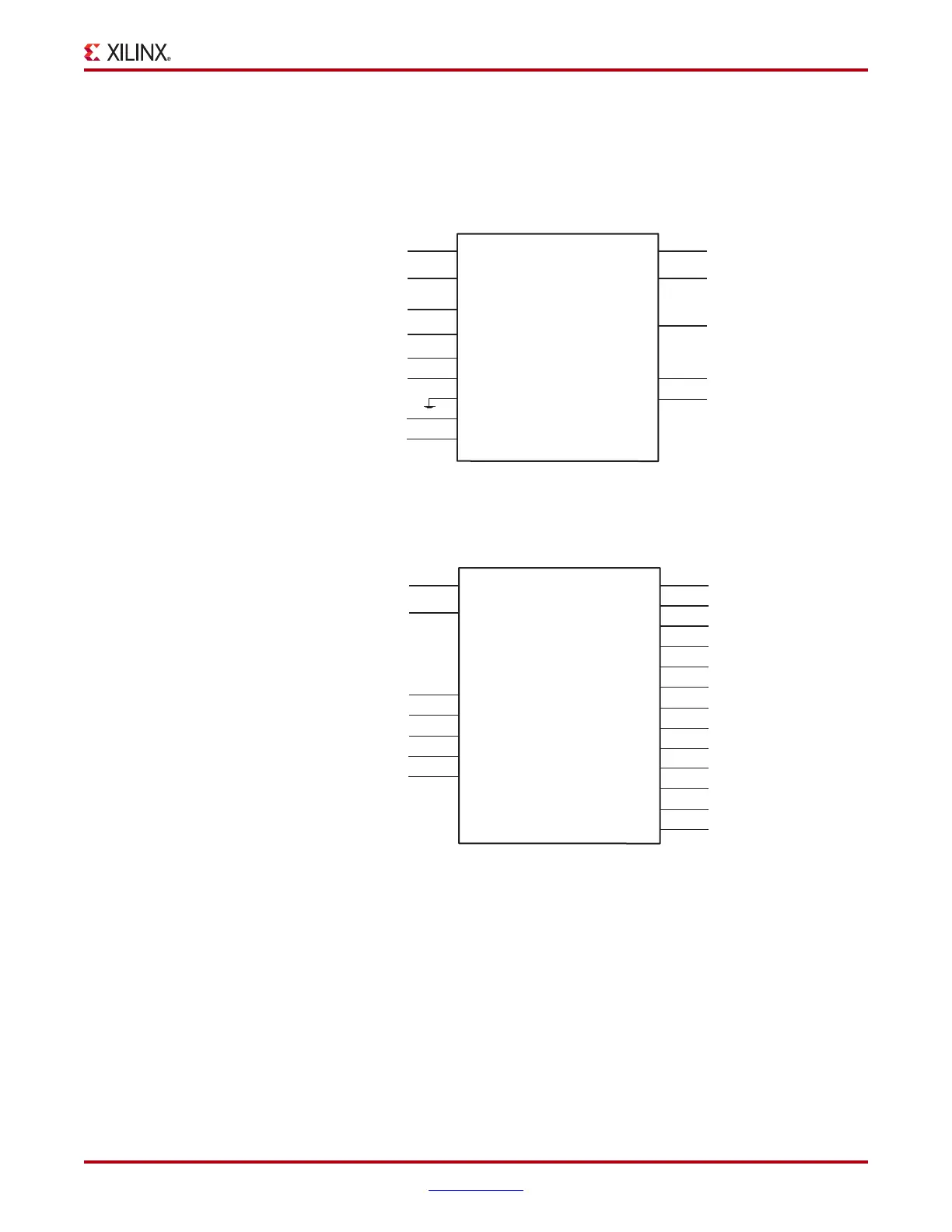

Block RAM and FIFO ECC Primitive

Figure 4-29 shows the block RAM (RAMB36SDP) ECC primitive. Figure 4-30 shows the

FIFO36_72 ECC primitive. The FIFO36_72 only supports standard mode.

X-Ref Target - Figure 4-29

Figure 4-29: RAMB36SDP: Block RAM ECC Primitive

X-Ref Target - Figure 4-30

Figure 4-30: FIFO36_72: FIFO ECC Primitive

SBITERR

DI[63:0]

WRADDR[8:0]

RDADDR[8:0]

SSR

WRCLK

DIP[7:0]

(Decode Only)

ECCPARITY[7:0]

(Standard or

Encode Only)

DBITERR

DO[63:0]

DOP[7:0]

WREN

RDEN

RDCLK

ug190_4_26_022207

RAMB36SDP

SBITERR

DI[63:0]

RST

WRCLK

DIP[7:0]

ECCPARITY[7:0]

DBITERR

DO[63:0]

DOP[7:0]

WREN

RDEN

RDCLK

ug190_4_34_022207

FIFO36_72

EMPTY

FULL

ALMOSTEMPTY

ALMOSTFULL

RDERR

WRERR

RDCOUNT[8:0]

WRCOUNT[8:0]

Loading...

Loading...