Virtex-5 FPGA User Guide www.xilinx.com 217

UG190 (v5.0) June 19, 2009

Chapter 6

SelectIO Resources

I/O Tile Overview

Input/output characteristics and logic resources are covered in three consecutive chapters.

Chapter 6, “SelectIO Resources” describes the electrical behavior of the output drivers and

input receivers, and gives detailed examples of many standard interfaces. Chapter 7,

“SelectIO Logic Resources,” describes the input and output data registers and their

Double-Data-Rate (DDR) operation, and the programmable input delay (IDELAY).

Chapter 8, “Advanced SelectIO Logic Resources,” describes the data

serializer/deserializer (SERDES).

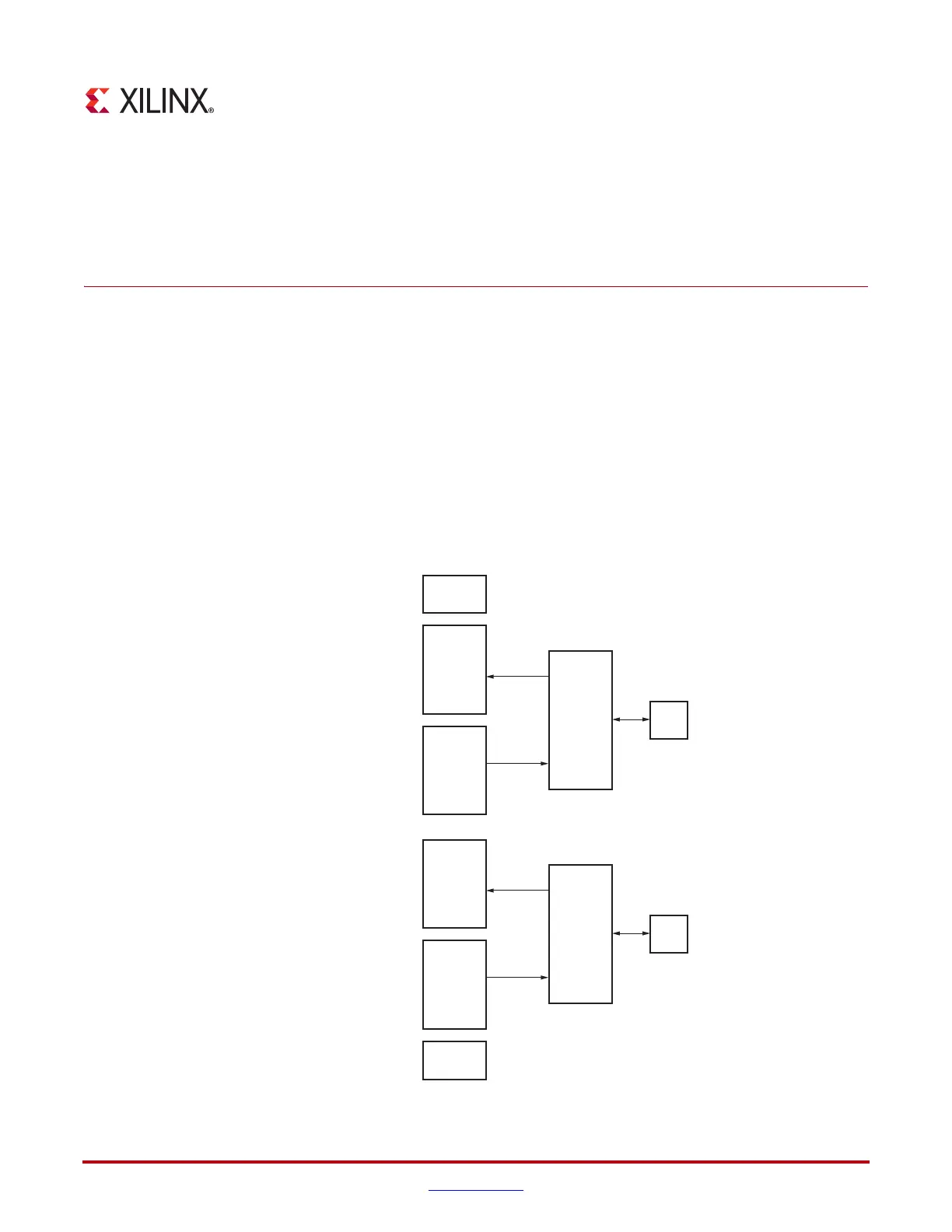

An I/O tile contains two IOBs, two ILOGICs, two OLOGICs, and two IODELAYs.

Figure 6-1 shows a Virtex-5 FPGA I/O tile.

X-Ref Target - Figure 6-1

Figure 6-1: Virtex-5 FPGA I/O Tile

ug190_6_01_041106

ILOGIC

(Chapter 7)

or

ISERDES

(Chapter 8)

OLOGIC

(Chapter 7)

or

OSERDES

(Chapter 8)

IODELAY

(Chapter 7)

IODELAY

(Chapter 7)

IOB

(Chapter 6)

Pad

ILOGIC

(Chapter 7)

or

ISERDES

(Chapter 8)

OLOGIC

(Chapter 7)

or

OSERDES

(Chapter 8)

IOB

(Chapter 6)

Pad

Loading...

Loading...