Virtex-5 FPGA User Guide www.xilinx.com 75

UG190 (v5.0) June 19, 2009

Application Examples

Application Examples

The Virtex-5 FPGA DCM can be used in a variety of creative and useful applications. The

following examples show some of the more common applications.

Standard Usage

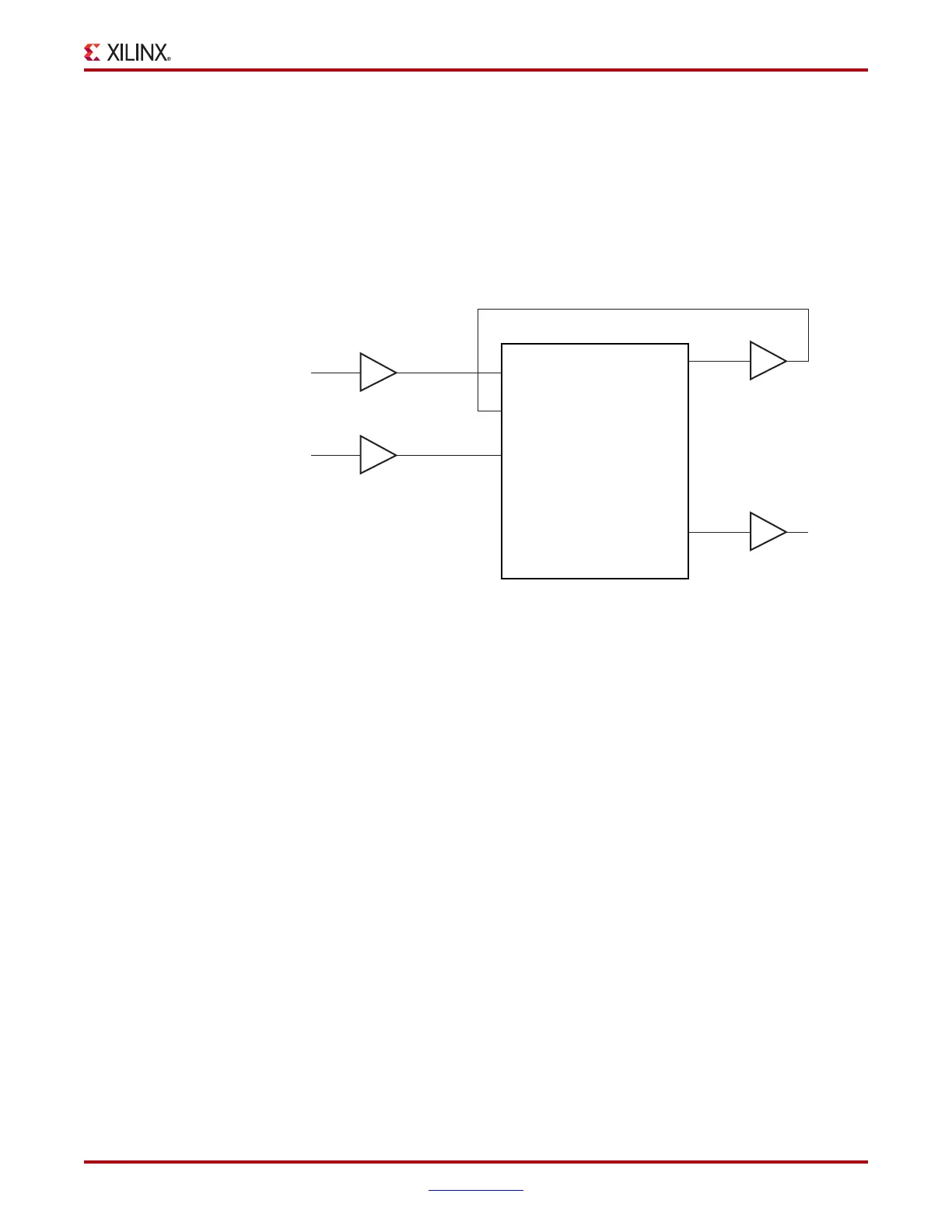

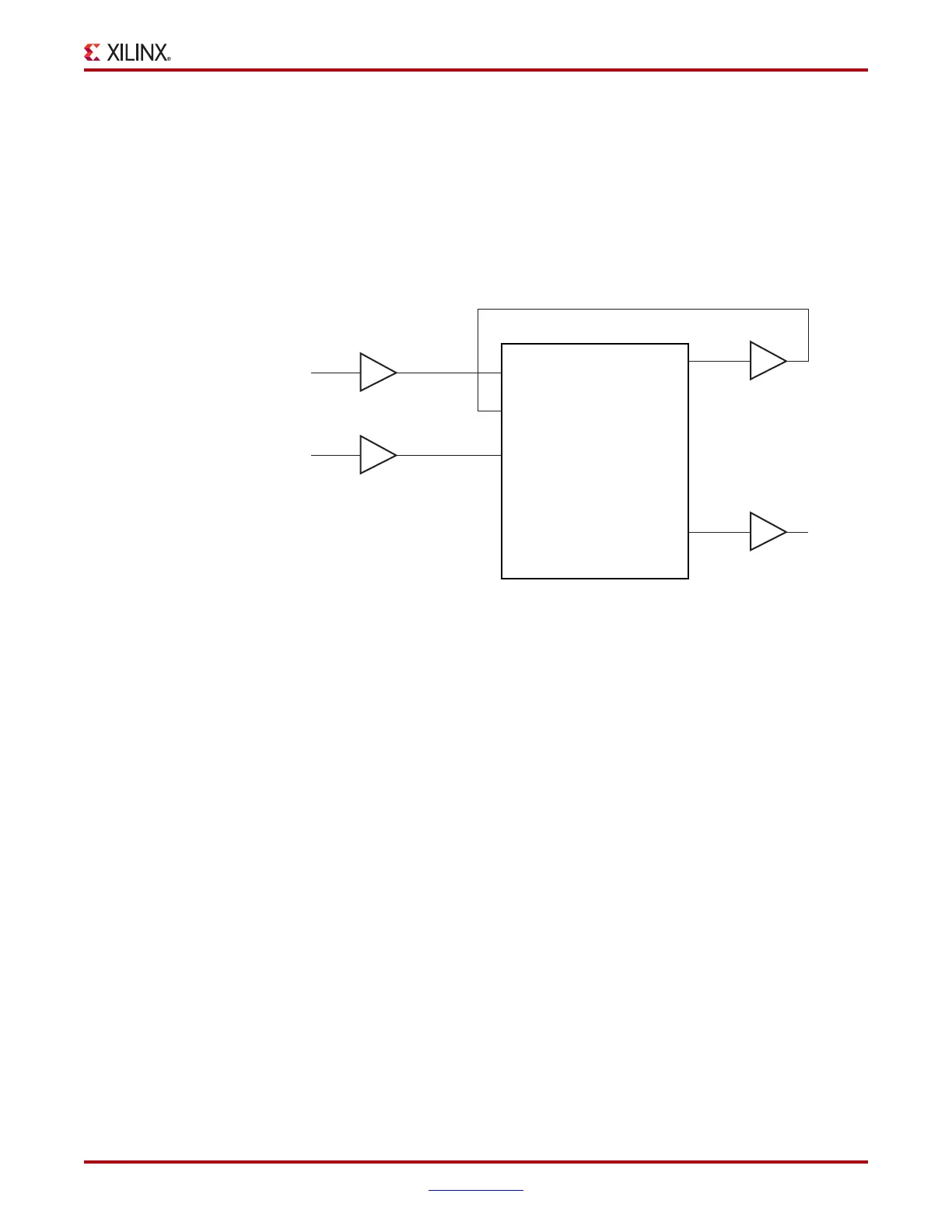

The circuit in Figure 2-8 shows DCM_BASE implemented with internal feedback and

access to RST and LOCKED pins. This example shows the simplest use case for a DCM.

Board-Level Clock Generation

The board-level clock generation example in Figure 2-9 illustrates how to use a DCM to

generate output clocks for other components on the board. This clock can then be used to

interface with other devices. In this example, a DDR register is used with its inputs

connected to GND and V

CC

. Because the output of the DCM is routed to BUFG, the clock

stays within global routing until it reaches the output register. The quality of the clock is

maintained.

The board-level clock generation example in Figure 2-10, with internal feedback, illustrates

the clock generation for a forwarded clock on the board.

X-Ref Target - Figure 2-8

Figure 2-8: Standard Usage

CLKIN

CLK0

CLK90

CLK180

CLK270

CLK2X

CLK2X180

CLKDV

CLKFX

CLKFX180

LOCKED

CLKFB

RST

IBUFG

DCM_BASE

IBUF

BUFG

OBUF

ug190_2_08_032506

Loading...

Loading...