76 www.xilinx.com Virtex-5 FPGA User Guide

UG190 (v5.0) June 19, 2009

Chapter 2: Clock Management Technology

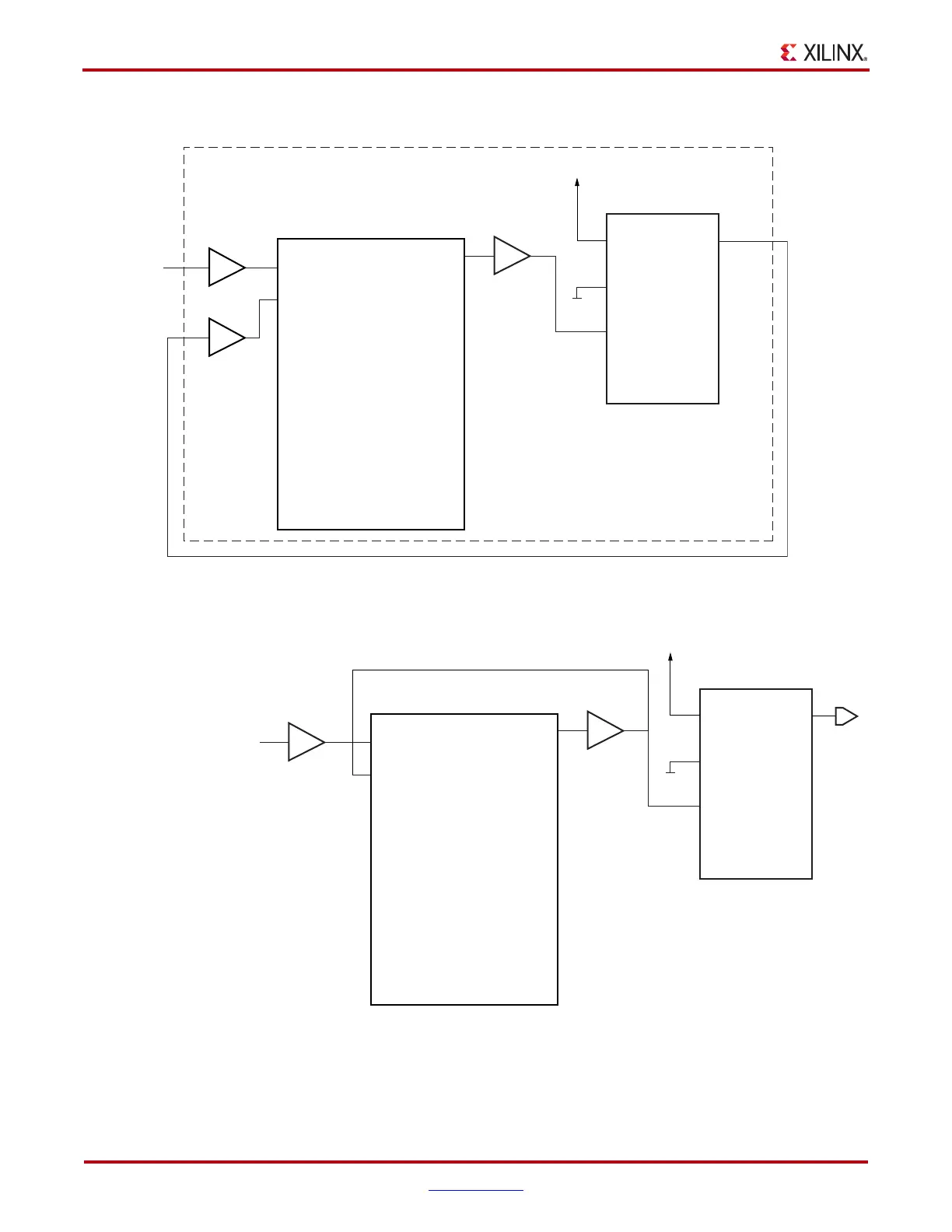

X-Ref Target - Figure 2-9

Figure 2-9: Board-Level Clock Using DDR Register with External Feedback

CLKIN

CLK0

D1

D2

GND

V

CC

C

Q

CLK90

CLK180

CLK270

CLK2X

CLK2X180

CLKDV

CLKFX

CLKFX180

LOCKED

DO(15:0)

CLKFB

IBUFG

DCM_ADV

ODDR

IBUFG

BUFG

UG190_2_09_042308

RST

PSINCDEC

PSEN

PSCLK

DADDR[6:0]

DI[15:0]

DWE

DEN

DCLK

Outside FPGA

Inside FPGA

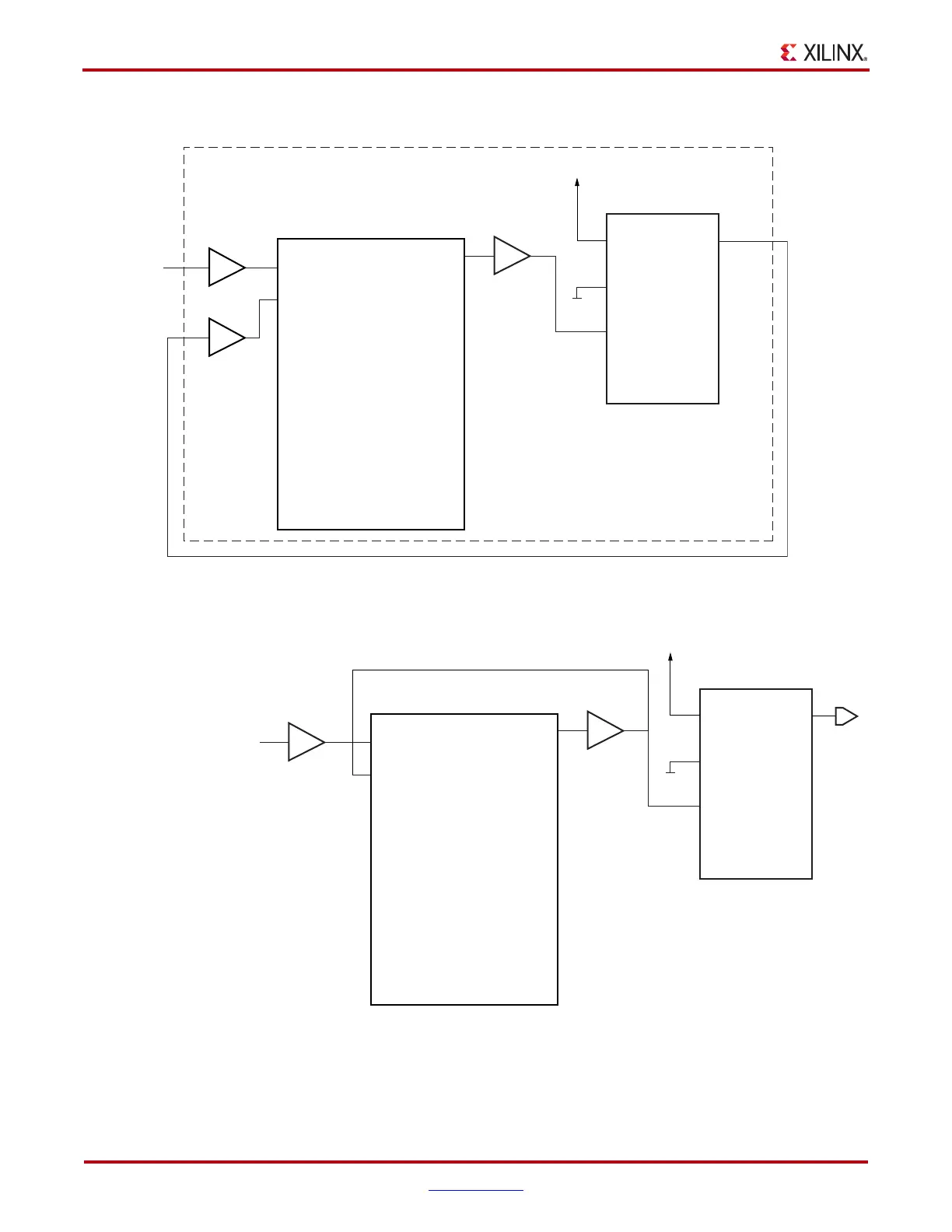

X-Ref Target - Figure 2-10

Figure 2-10: Board-Level Clock with Internal Feedback

CLKIN

CLK0

D1

D2

GND

V

CC

C

Q

CLK90

CLK180

CLK270

CLK2X

CLK2X180

CLKDV

CLKFX

CLKFX180

LOCKED

DO(15:0)

CLKFB

IBUFG

DCM_ADV

ODDR

BUFG

ug190_2_11_032506

RST

PSINCDEC

PSEN

PSCLK

DADDR[6:0]

DI[15:0]

DWE

DEN

DCLK

Loading...

Loading...