Virtex-5 FPGA User Guide www.xilinx.com 297

UG190 (v5.0) June 19, 2009

Specific Guidelines for I/O Supported Standards

Differential LVPECL (Low-Voltage Positive Emitter-Coupled Logic)

LVPECL is a very popular and powerful high-speed interface in many system applications.

Virtex-5 FPGA I/Os are designed to comply with the EIA/TIA electrical specifications for

2.5V LVPECL to make system and board design easier.

LVPECL Transceiver Termination

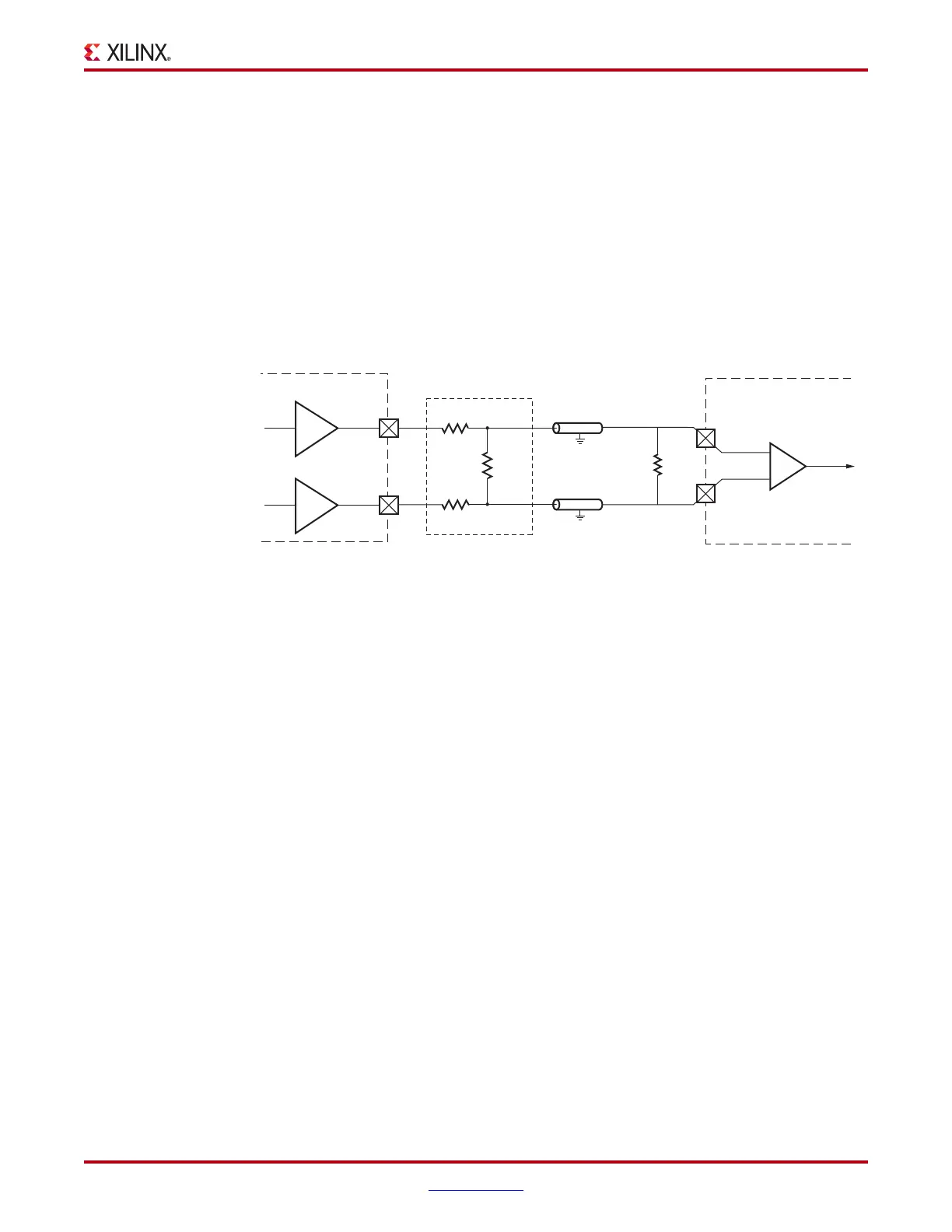

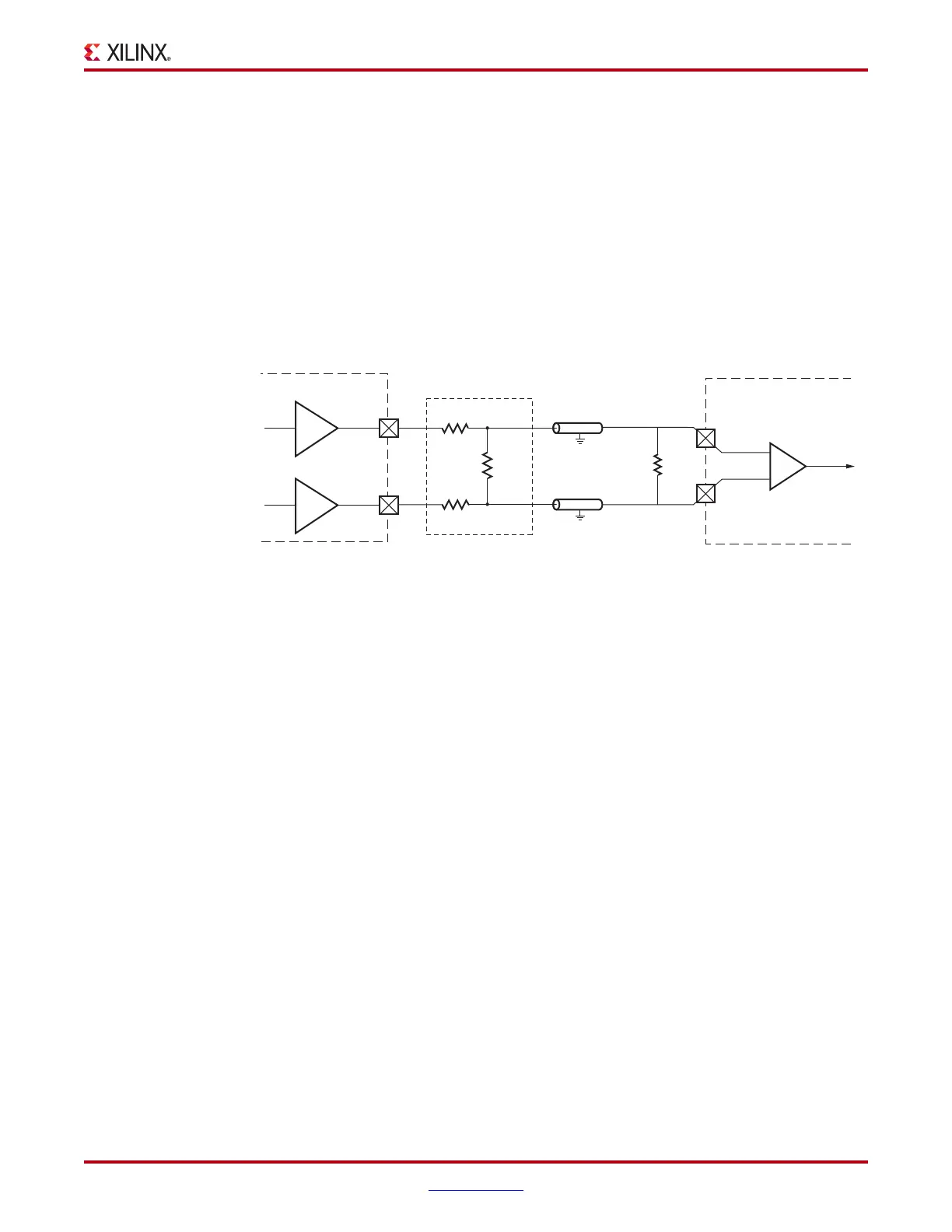

The Virtex-5 FPGA LVPECL transmitter and receiver requires the termination shown in

Figure 6-90, illustrating a Virtex-5 FPGA LVPECL transmitter and receiver on a board with

50 Ω transmission lines. The LVPECL driver is composed of two LVCMOS drivers that

form a compliant LVPECL output when combined with the three resistor output

termination circuit.

X-Ref Target - Figure 6-90

Figure 6-90: LVPECL Transmitter Termination

ug190_6_84_030506

Z

0

= 50Ω

Z

0

= 50Ω

R

DIV

187Ω

R

DIFF

= 100Ω

R

S

70Ω

R

S

70Ω

IN

INX

Data in

-

+

LVPECL_25

IOB

LVPECL_25

LVPECL_25

IOB

Loading...

Loading...