198 www.xilinx.com Virtex-5 FPGA User Guide

UG190 (v5.0) June 19, 2009

Chapter 5: Configurable Logic Blocks (CLBs)

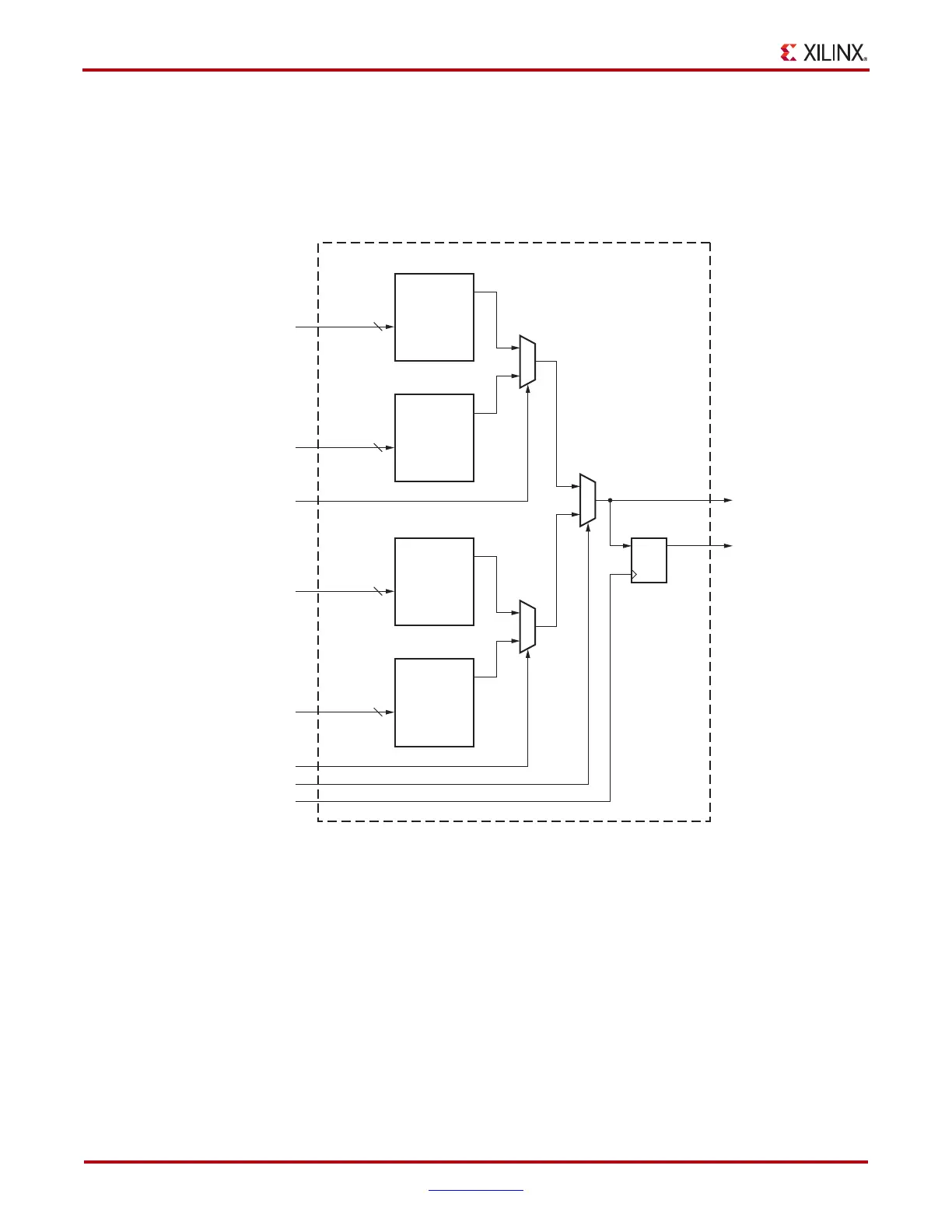

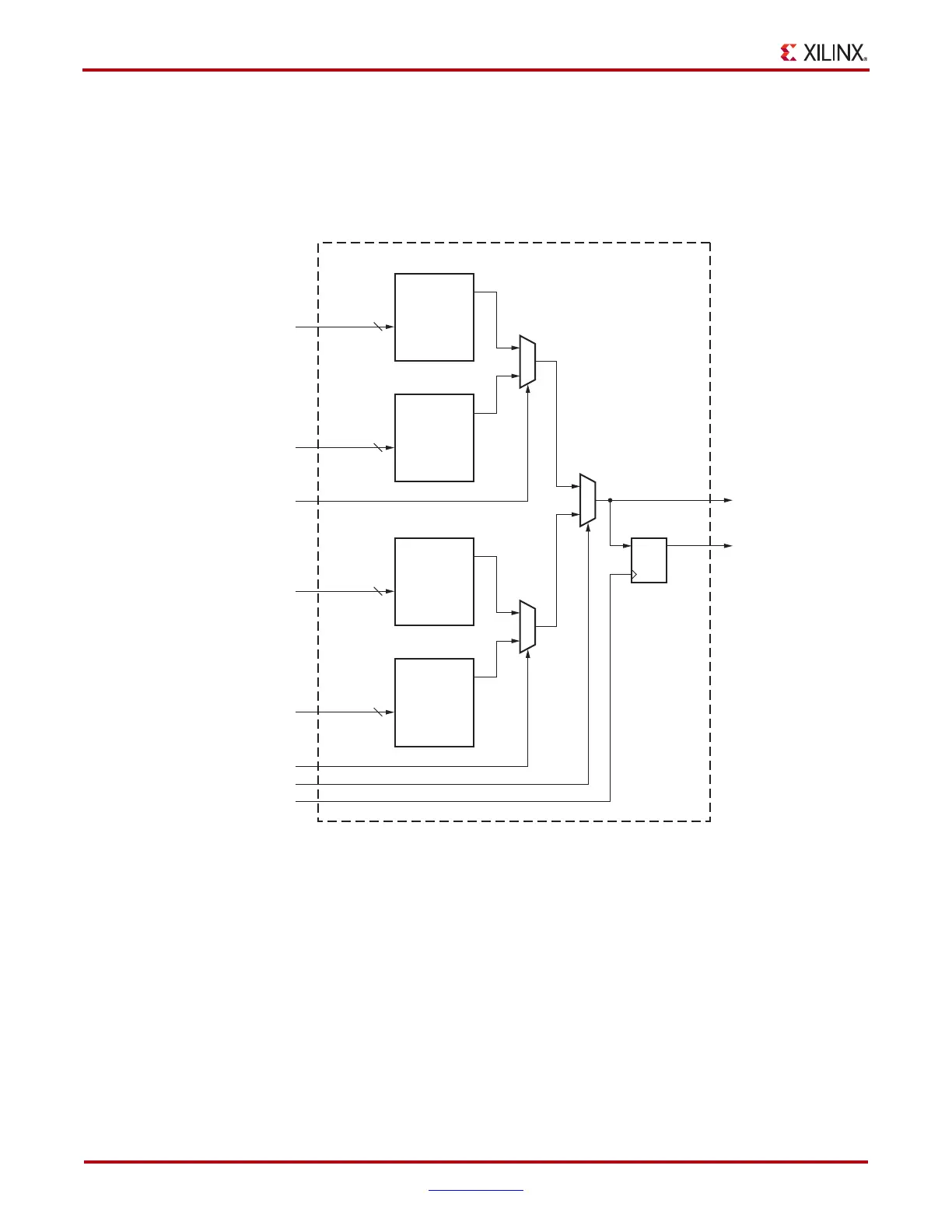

16:1 Multiplexer

Each slice has an F8MUX. F8MUX combines the outputs of F7AMUX and F7BMUX to form

a combinatorial function up to 27 inputs (or a 16:1 MUX). Only one 16:1 MUX can be

implemented in a slice, as shown in Figure 5-23.

It is possible to create multiplexers wider than 16:1 across more than one SLICEM.

However, there are no direct connections between slices to form these wide multiplexers.

Fast Lookahead Carry Logic

In addition to function generators, dedicated carry logic is provided to perform fast

arithmetic addition and subtraction in a slice. A Virtex-5 FPGA CLB has two separate carry

chains, as shown in Figure 5-1. The carry chains are cascadable to form wider add/subtract

logic, as shown in Figure 5-2.

The carry chain in the Virtex-5 device is running upward and has a height of four bits per

slice. For each bit, there is a carry multiplexer (MUXCY) and a dedicated XOR gate for

adding/subtracting the operands with a selected carry bits. The dedicated carry path and

X-Ref Target - Figure 5-23

Figure 5-23: 16:1 Multiplexer in a Slice

UG190_5_23_050506

(D[6:1])

(C[6:1])

(CX)

(B[6:1])

(A[6:1])

(AX)

(BX)

(CLK)

SELF7

SELF7

SELF8

CLK

6

SLICE

LUT

LUT

LUT

LUT

A[6:1]

O6

6

A[6:1]

O6

Registered

Output

16:1 MUX

Output

(Optional)

DQ

(BMUX)

(B)

6

A[6:1]

O6

6

A[6:1]

O6

F7BMUX

F8MUX

F7AMUX

SEL D [1:0], DATA D [3:0]

Input

SEL C [1:0], DATA C [3:0]

Input

SEL B [1:0], DATA B [3:0]

Input

SEL A [1:0], DATA A [3:0]

Input

Loading...

Loading...