Virtex-5 FPGA User Guide www.xilinx.com 197

UG190 (v5.0) June 19, 2009

CLB Overview

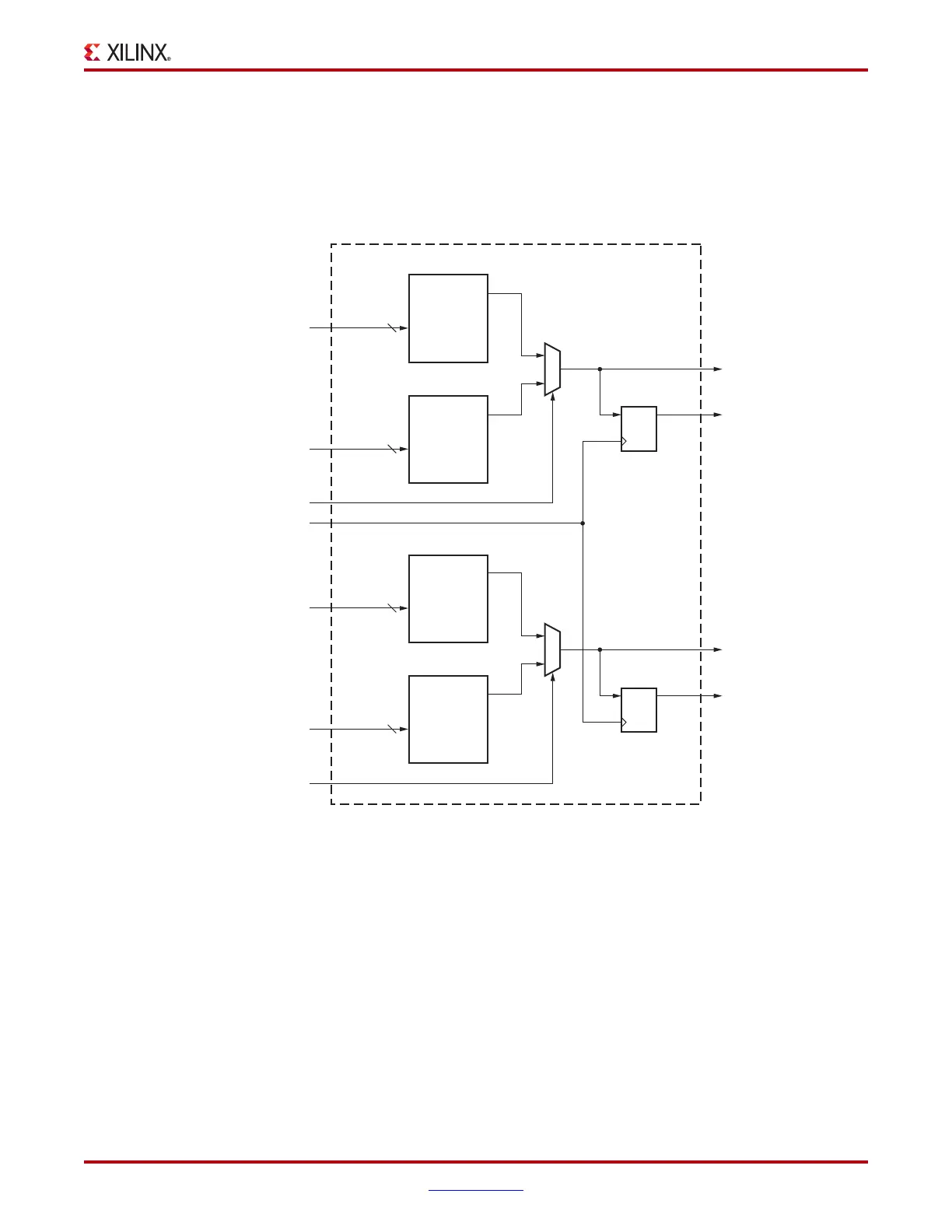

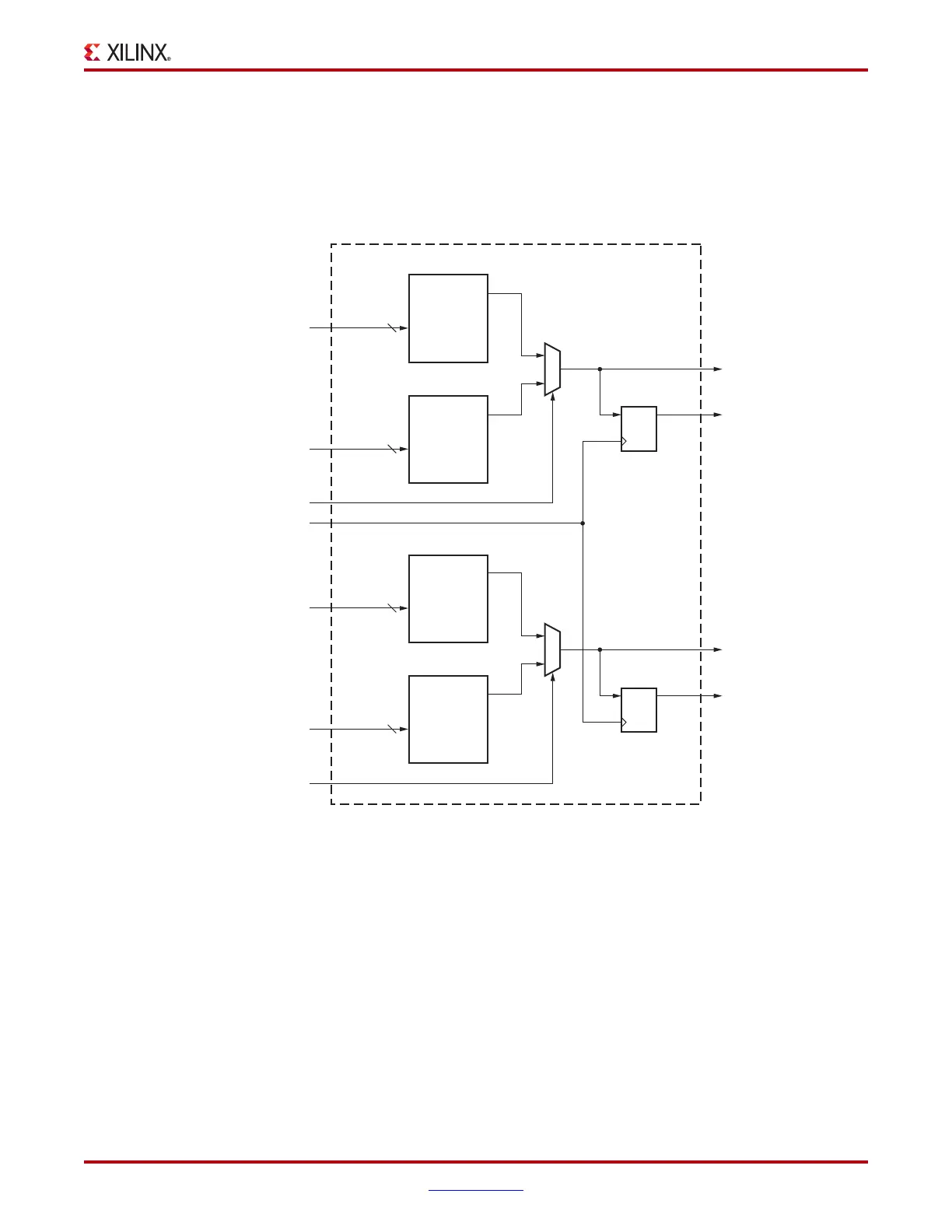

8:1 Multiplexer

Each slice has an F7AMUX and an F7BMUX. These two muxes combine the output of two

LUTs to form a combinatorial function up to 13 inputs (or an 8:1 MUX). Up to two 8:1

MUXes can be implemented in a slice, as shown in Figure 5-22.

X-Ref Target - Figure 5-22

Figure 5-22: Two 8:1 Multiplexers in a Slice

UG190_5_22_090806

(D[6:1])

(C[6:1])

(CX)

(B[6:1])

(A[6:1])

(AX)

SELF7(1)

(CLK)

CLK

SELF7(2)

SEL D [1:0], DATA D [3:0]

Input (1)

SEL C [1:0], DATA C [3:0]

Input (1)

SEL B [1:0], DATA B [3:0]

Input (2)

SEL A [1:0], DATA A [3:0]

Input (2)

6

SLICE

LUT

LUT

LUT

LUT

A[6:1]

O6

6

A[6:1]

O6

Registered

Output

8:1 MUX

Output (1)

(Optional)

DQ

(CMUX)

(CQ)

Registered

Output

8:1 MUX

Output (2)

(Optional)

DQ

(AMUX)

(AQ)

6

A[6:1]

O6

6

A[6:1]

O6

F7BMUX

F7AMUX

Loading...

Loading...