Virtex-5 FPGA User Guide www.xilinx.com 143

UG190 (v5.0) June 19, 2009

FIFO Port Descriptions

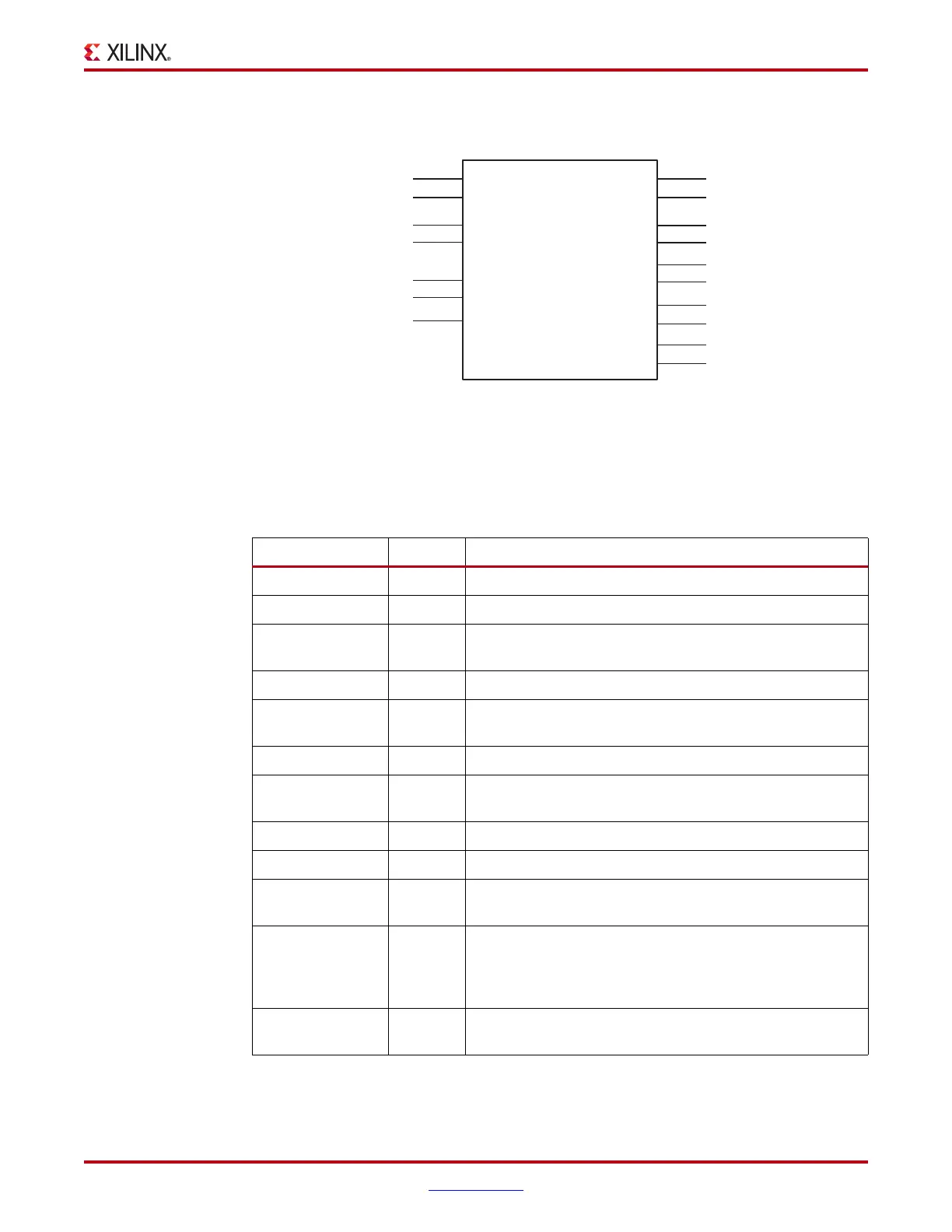

Figure 4-19 shows the FIFO18 primitive.

FIFO Port Descriptions

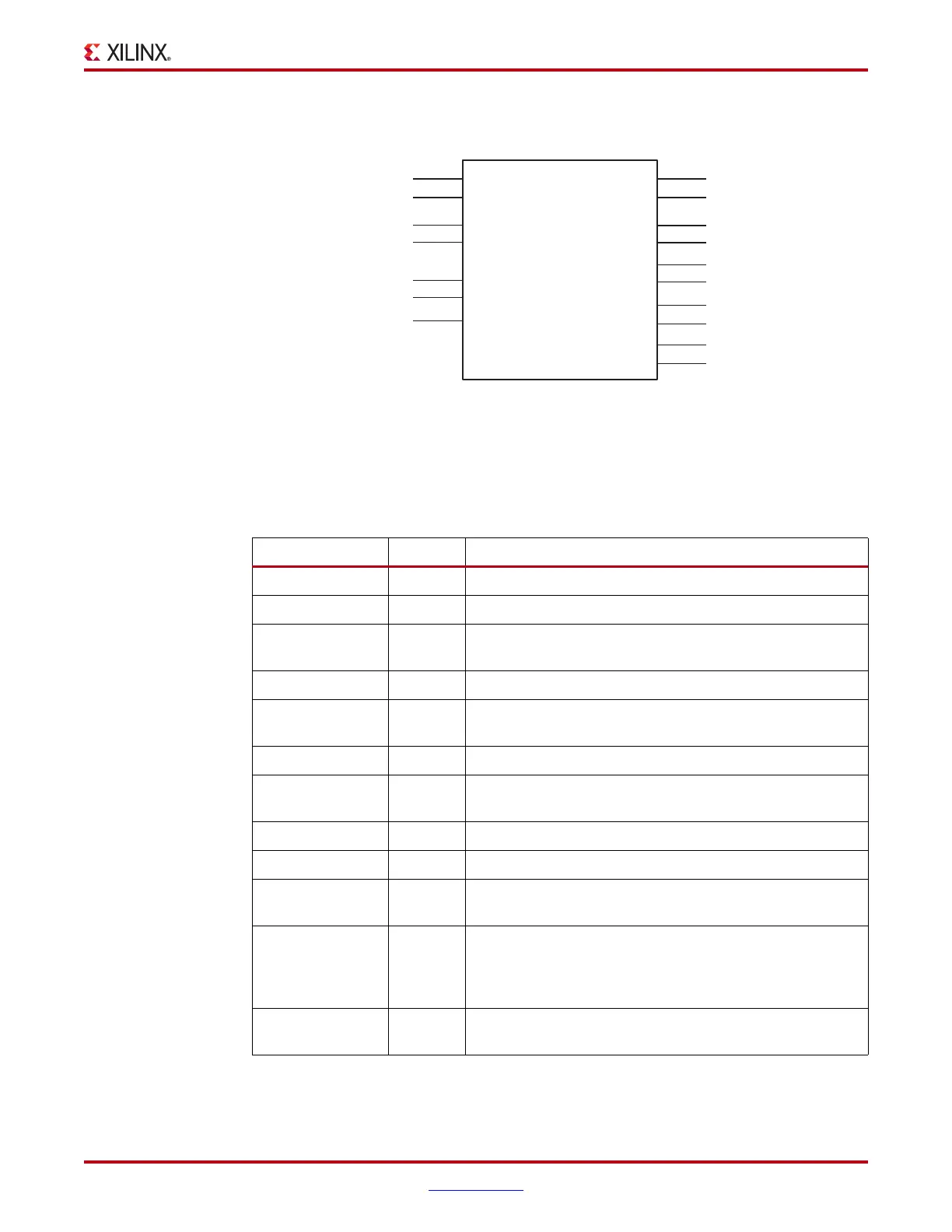

Table 4-15 lists the FIFO I/O port names and descriptions.

X-Ref Target - Figure 4-19

Figure 4-19: FIFO18 Primitive

DOP[1:0]

DI[15:0]

DIP[1:0]

RDEN

RST

RDCLK

WREN

WRCLK

DO[15:0]

RDCOUNT[11:0]

WRCOUNT[11:0]

EMPTY

FULL

ALMOSTEMPTY

ALMOSTFULL

WRERR

RDERR

FIFO18

ug190_4_15_040606

Table 4-15: FIFO I/O Port Names and Descriptions

Port Name Direction Description

DI Input Data input.

DIP Input Parity-bit input.

WREN Input Write enable. When WREN = 1, data will be written to

memory. When WREN = 0, write is disabled.

WRCLK Input Clock for write domain operation.

RDEN Input Read enable. When RDEN = 1, data will be read to output

register. When RDEN = 0, read is disabled.

RDCLK Input Clock for read domain operation.

RESET Input Asynchronous reset of all FIFO functions, flags, and

pointers. RESET must be asserted for three clock cycles.

DO Output Data output, synchronous to RDCLK.

DOP Output Parity-bit output, synchronous to RDCLK.

FULL Output All entries in FIFO memory are filled. No additional writes

are accepted. Synchronous to WRCLK.

ALMOSTFULL Output Almost all entries in FIFO memory have been filled.

Synchronous to WRCLK. The offset for this flag is user

configurable. See Table 4-16 for the clock latency for flag

deassertion.

EMPTY Output FIFO is empty. No additional reads are accepted.

Synchronous to RDCLK.

Loading...

Loading...