Virtex-5 FPGA User Guide www.xilinx.com 81

UG190 (v5.0) June 19, 2009

Application Examples

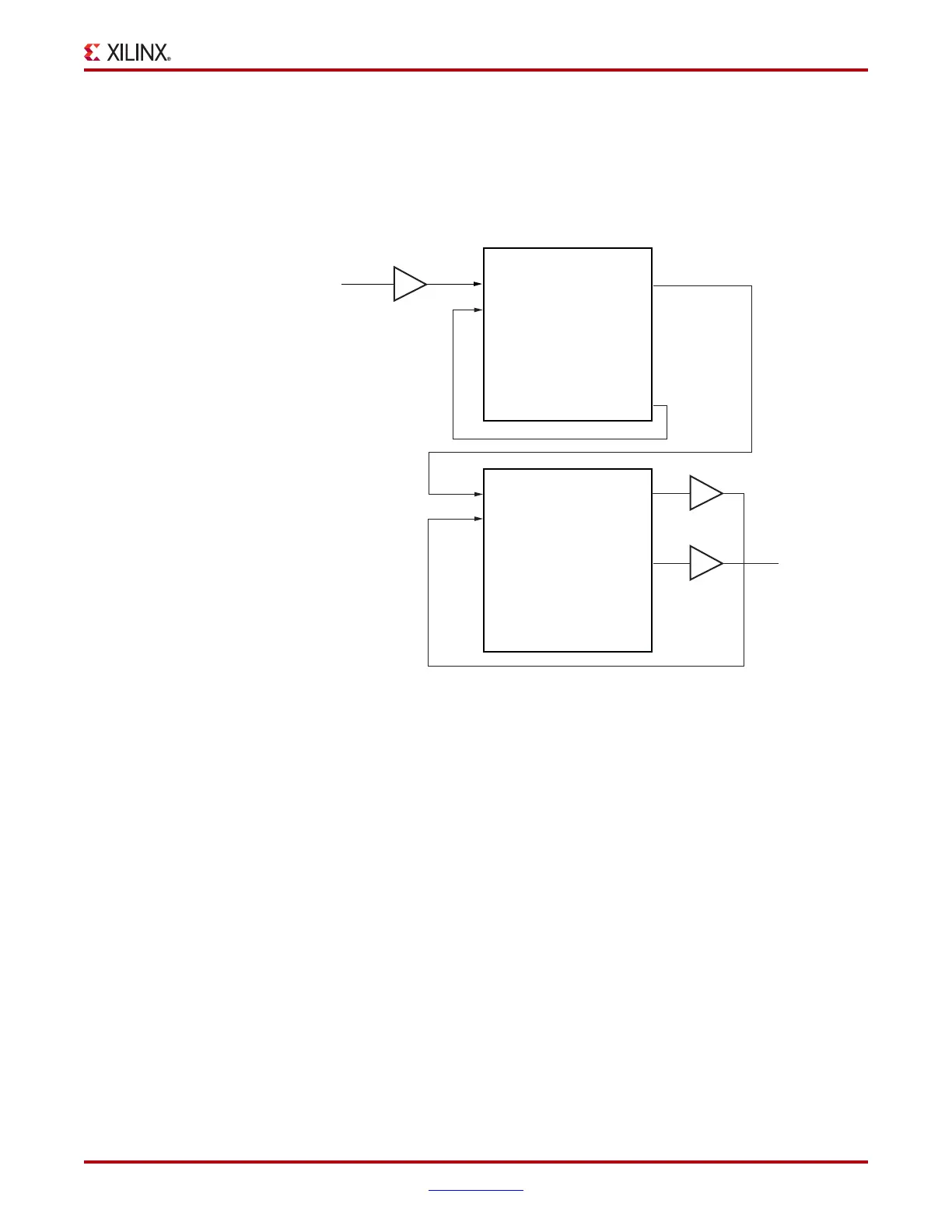

DCM with PLL

The PLL can be used to drive the DCM to reduce the source clock’s incoming jitter before

inputting DCM. This setup reduces the source clock jitter while enabling user access to all

available DCM clock outputs. Figure 2-14 illustrates the PLL driving a DCM within the

same CMT block using the dedicated routing resource (without BUFG).

X-Ref Target - Figure 2-14

Figure 2-14: PLL Driving DCM

CLKIN CLK0

CLK90

CLK180

CLK270

CLK2X

CLK2X180

CLKDV

CLKFX180

CLKFX

CLKFBIN

DCM

BUFG

BUFG

ug190_2_15_040906

IBUFG

CLKIN1 CLKOUT0

CLKOUT1

CLKOUT2

CLKOUT3

CLKOUT4

CLKOUT5

CLKFBOUT

RST

RST

CLKFBIN

PLL

Loading...

Loading...