160 www.xilinx.com Virtex-5 FPGA User Guide

UG190 (v5.0) June 19, 2009

Chapter 4: Block RAM

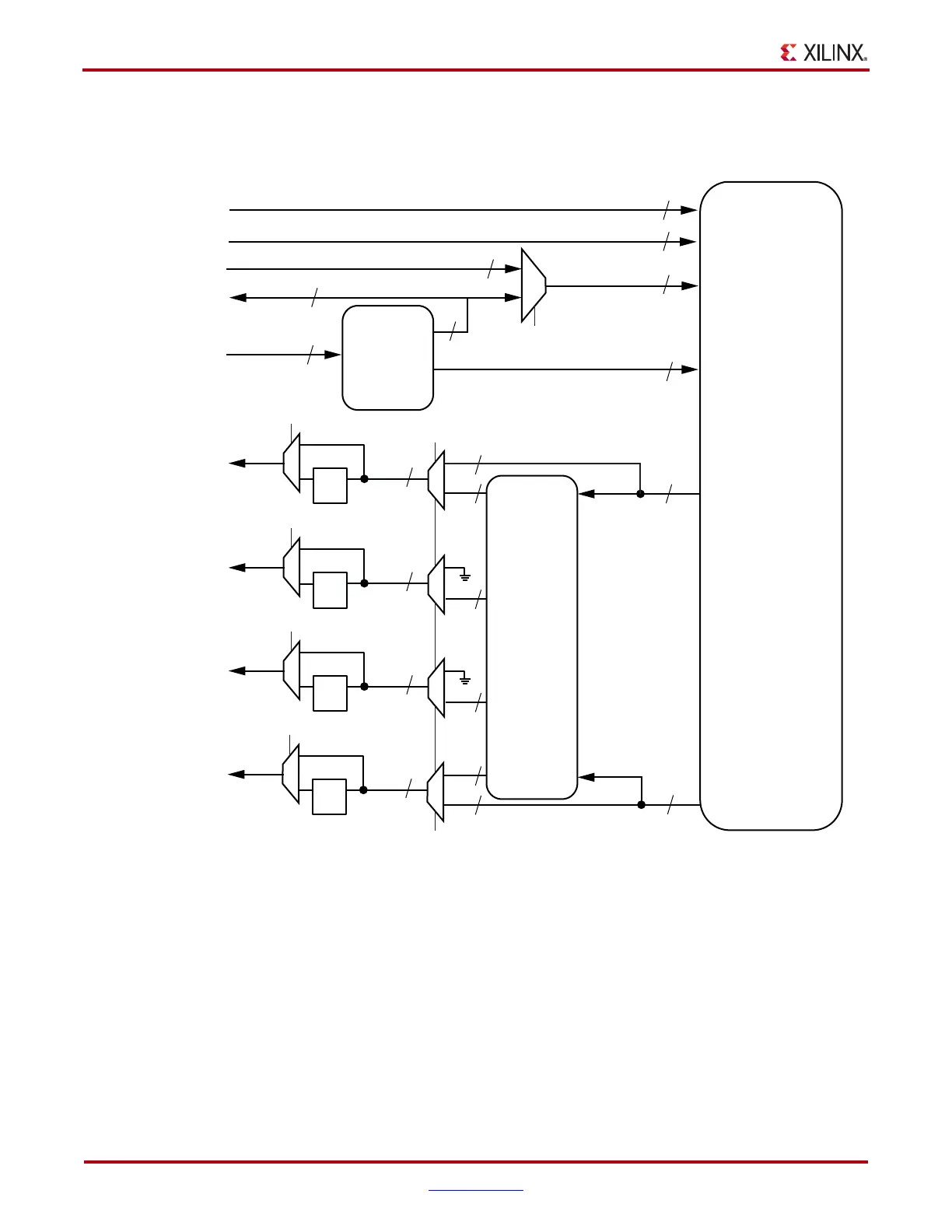

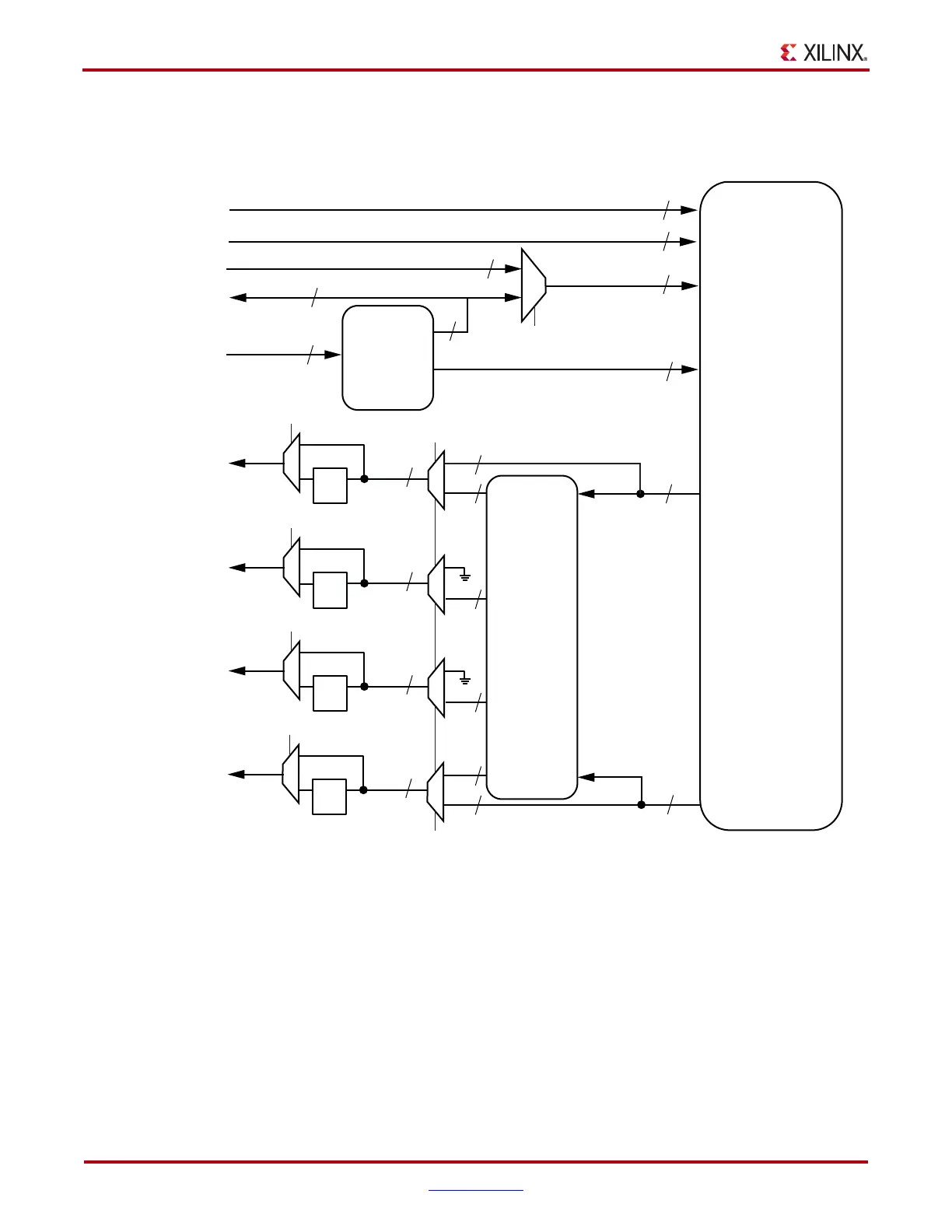

Top-Level View of the Block RAM ECC Architecture

Figure 4-28 shows the top-level view of a Virtex-5 FPGA block RAM in ECC mode.

X-Ref Target - Figure 4-28

Figure 4-28: Top-Level View of Block RAM ECC

wraddr

9

Data In

EN_ECC_WRITE

EN_ECC_READ

EN_ECC_READ

Data

Out

Parity

Out

rdaddr

9

Block RAM

512 x 72

64-bit

ECC

Encode

64

64

64

DI[63:0]

DO[63:0]

0

1

Decode

and

Correct

64

64

RDADDR[8:0]

WRADDR[8:0]

8

DOP[7:0]

8

ECCPARITY[7:0]

8

8

DIP[7:0]

8

UG190_c4_25_022609

8

0

1

0

1

8

1

0

1

0

1

1

DO_REG

0

1

64

QD

DBITERR

DO_REG

0

1

1

QD

SBITERR

DO_REG

0

1

1

QD

DO_REG

0

1

8

QD

Loading...

Loading...