360 www.xilinx.com Virtex-5 FPGA User Guide

UG190 (v5.0) June 19, 2009

Chapter 8: Advanced SelectIO Logic Resources

NUM_CE Attribute

The NUM_CE attribute defines the number of clock enables (CE1 and CE2) used. The

possible values are 1 and 2 (default = 2).

SERDES_MODE Attribute

The SERDES_MODE attribute defines whether the ISERDES_NODELAY module is a

master or slave when using width expansion. The possible values are MASTER and

SLAVE. The default value is MASTER. See “ISERDES Width Expansion.”

ISERDES_NODELAY Clocking Methods

Networking Interface Type

The phase relationship of CLK and CLKDIV is important in the serial-to-parallel

conversion process. CLK and CLKDIV are (ideally) phase-aligned within a tolerance.

There are several clocking arrangements within the FPGA to help the design meet the

phase relationship requirements of CLK and CLKDIV. The only valid clocking

arrangements for the ISERDES_NODELAY block using the networking interface type are:

• CLK driven by BUFIO, CLKDIV driven by BUFR

• CLK driven by DCM, CLKDIV driven by the CLKDV output of the same DCM

• CLK driven by PLL, CLKDIV driven by CLKOUT[0:5] of same PLL

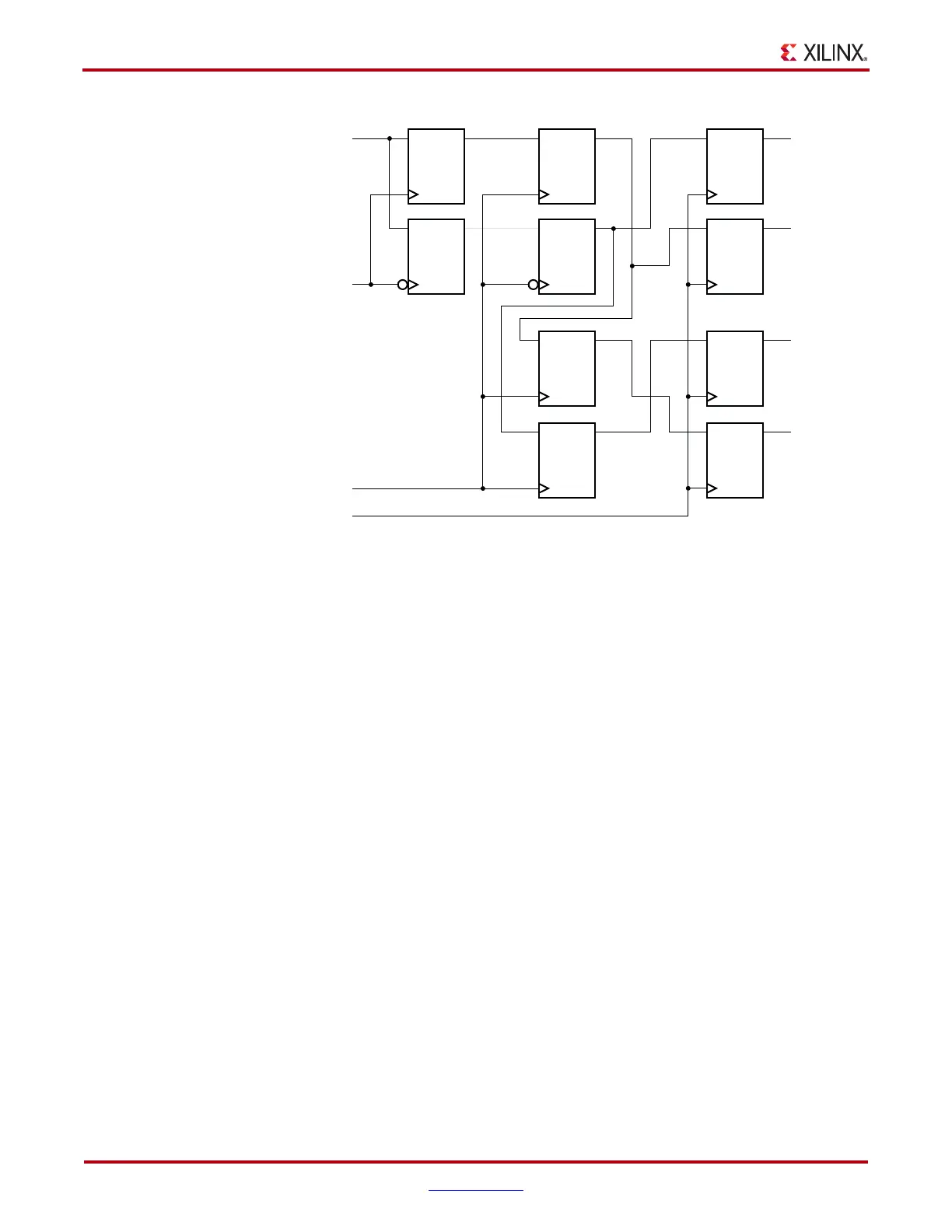

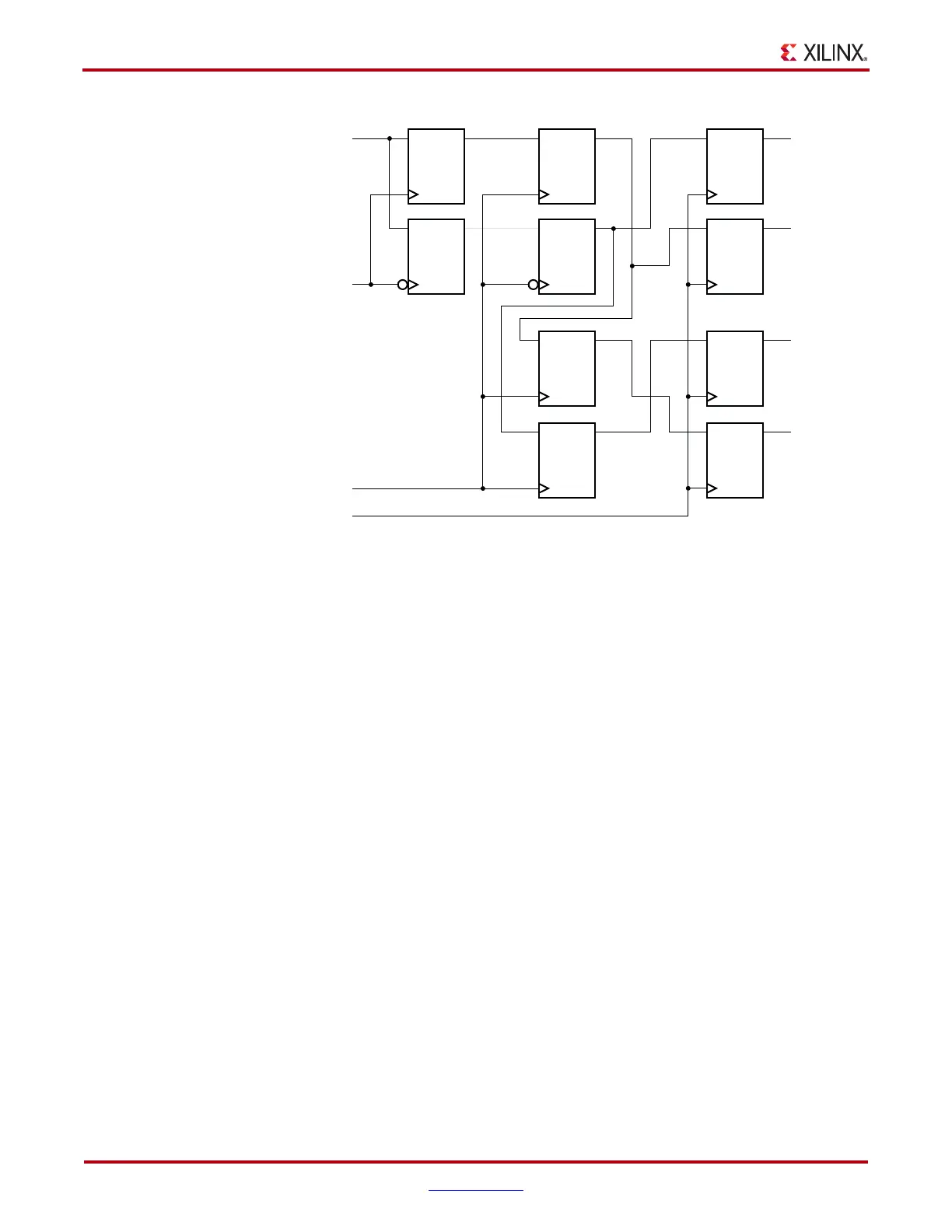

X-Ref Target - Figure 8-5

Figure 8-5: Internal Connections of ISERDES_NODELAY When in Memory Mode

Q1D

CLK

ICE

ICE

ICE

ICE

OCLK

CLKDIV

Q2

Q3

Q4

ug190_8_05_100307

FF0 FF2 FF6

FF1 FF3 FF7

FF4 FF8

FF5 FF9

Loading...

Loading...