74 www.xilinx.com Virtex-5 FPGA User Guide

UG190 (v5.0) June 19, 2009

Chapter 2: Clock Management Technology

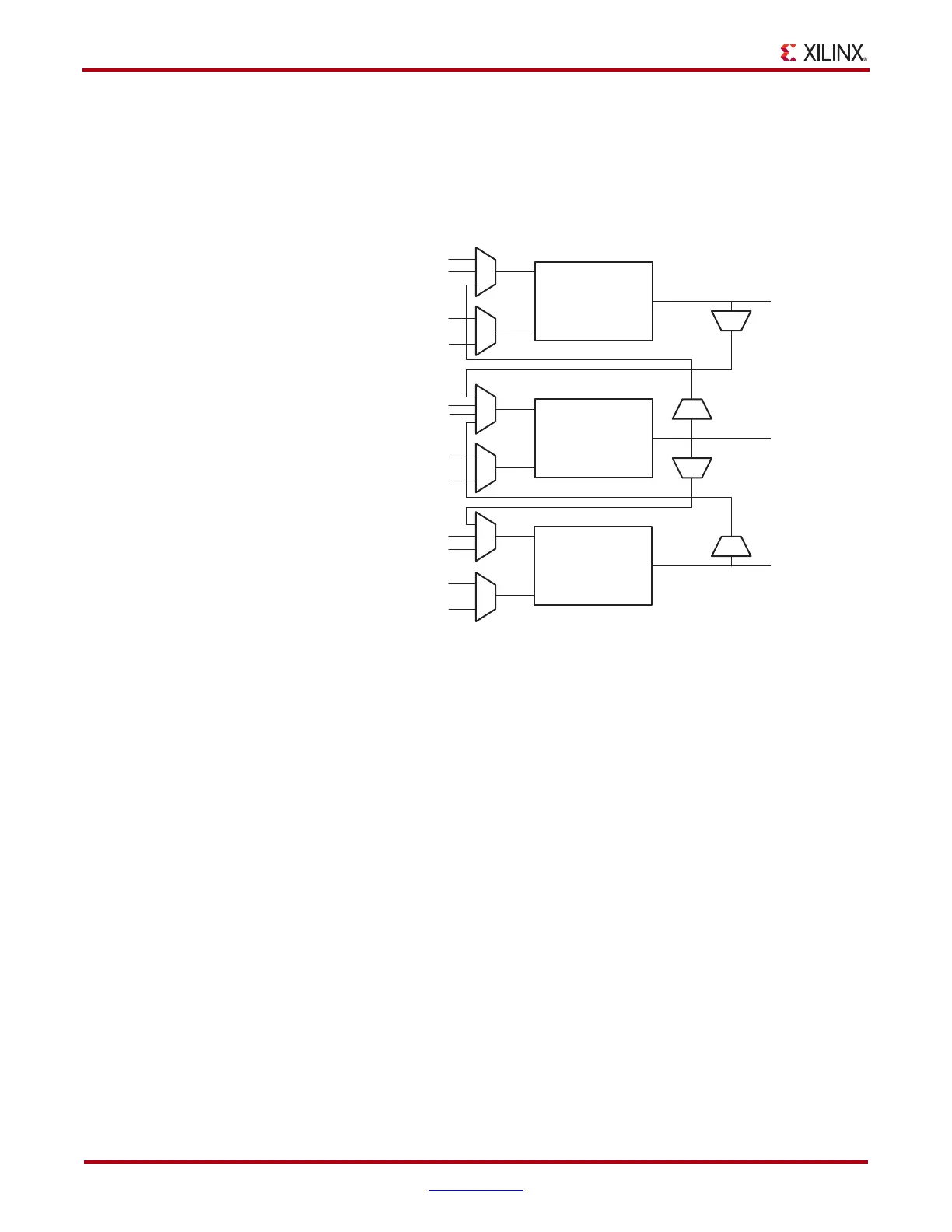

PLL To and From DCM

Figure 2-7 summarizes the dedicated connection between the DCM and the PLL in the

same CMT block. The PLL can drive either DCM in the same CMT block using a dedicated

connection. Similarly, the DCM can drive the PLL within the same CMT block with a

dedicated connection. There is no BUFGCTRL required between the PLL and the DCM.

DCM To and From PMCD

The PMCD block is not available in the Virtex-5 devices. However, a limited retargeting

using the PLL is possible. Refer to “PLL in Virtex-4 FPGA PMCD Legacy Mode” in

Chapter 3 for more information.

X-Ref Target - Figure 2-7

Figure 2-7: DCM and PLL Connection in Same CMT Block

PLL

CLKIN

CLKFBIN

DCM1

CLKIN

CLKFB

DCM2

ug190_2_07_072307

CLKIN

CLKFB

To Global

Routing (BUFG)

To Global

Routing (BUFG)

To Global

Routing (BUFG)

PLL to DCM Input

PLL to DCM Input

DCM to PLL Input

DCM to PLL Input

From any IBUFG implementation

From any BUFG implementation

Loading...

Loading...