Virtex-5 FPGA User Guide www.xilinx.com 201

UG190 (v5.0) June 19, 2009

CLB / Slice Timing Models

General Slice Timing Model and Parameters

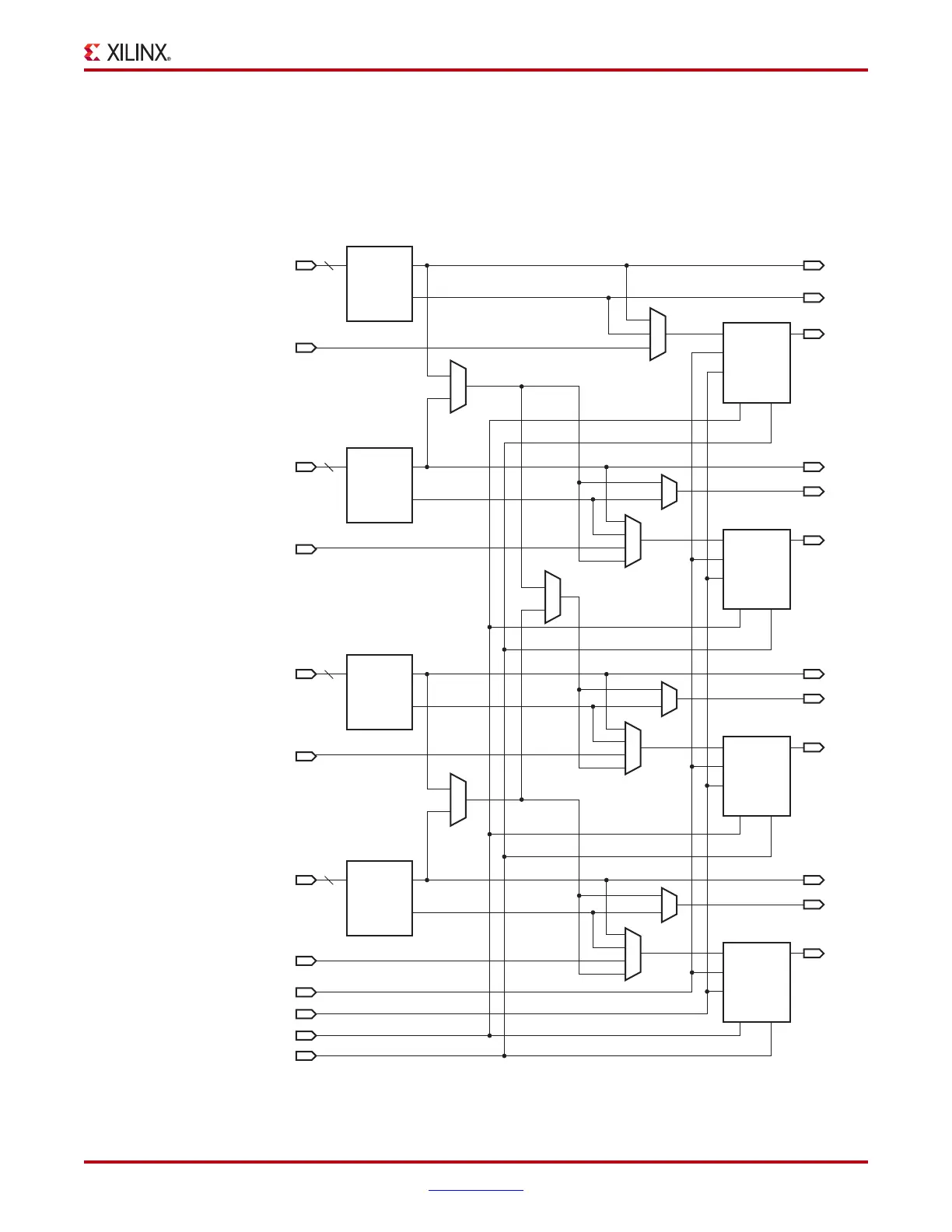

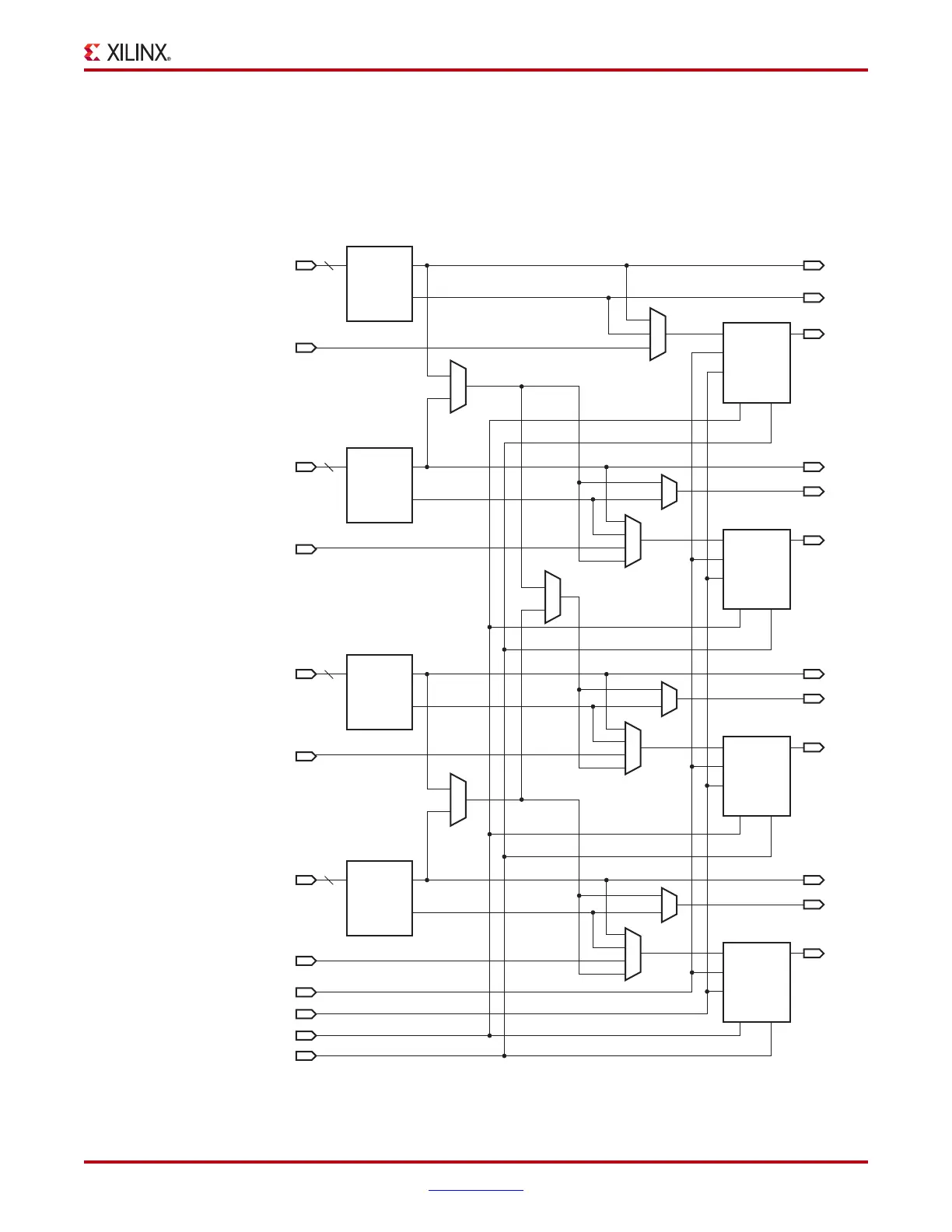

A simplified Virtex-5 FPGA slice is shown in Figure 5-25. Some elements of the slice are

omitted for clarity. Only the elements relevant to the timing paths described in this section

are shown.

X-Ref Target - Figure 5-25

Figure 5-25: Simplified Virtex-5 FPGA Slice

UG190_5_25_050506

LUT

O6

O5

6

D

FE/LAT

D

CE

CLK

SR REV

Q

F7BMUX

F8MUX

DMUX

DQ

D

Inputs

LUT

O6

O5

6

C

FE/LAT

D

CE

CLK

SR REV

Q

CQ

CMUX

C

Inputs

DX

CX

LUT

O6

O5

6

B

FE/LAT

D

CE

CLK

SR REV

Q

BQ

BMUX

B

Inputs

BX

FE/LAT

D

CE

CLK

SR REV

Q

AQ

F7AMUX

LUT

O6

O5

6

A

AMUX

A

Inputs

AX

CE

CLK

SR

REV

(DX)

Loading...

Loading...