358 www.xilinx.com Virtex-5 FPGA User Guide

UG190 (v5.0) June 19, 2009

Chapter 8: Advanced SelectIO Logic Resources

frequency domain. Therefore, RST should be driven High for a minimum of one CLKDIV

cycle.

When building an interface consisting of multiple ISERDES_NODELAY ports, all

ISERDES_NODELAY ports in the interface must be synchronized. The internal retiming of

the RST input is designed so that all ISERDES_NODELAY blocks that receive the same

reset pulse come out of reset synchronized with one another. The reset timing of multiple

ISERDES_NODELAY ports is shown in Figure 8-9, page 365.

ISERDES_NODELAY Attributes

Table 8-2 summarizes all the applicable ISERDES_NODELAY attributes. A detailed

description of each attribute follows the table. For more information on applying these

attributes in UCF, VHDL, or Verilog code, refer to the Xilinx ISE Software Manual.

BITSLIP_ENABLE Attribute

The BITSLIP_ENABLE attribute enables the Bitslip submodule. The possible values are

TRUE and FALSE (default). BITSLIP_ENABLE must be set to TRUE when

INTERFACE_TYPE is NETWORKING and FALSE when INTERFACE_TYPE is MEMORY.

When set to TRUE, the Bitslip submodule responds to the BITSLIP signal. When set to

FALSE, the Bitslip submodule is bypassed. See “BITSLIP Submodule.”

DATA_RATE Attribute

The DATA_RATE attribute defines whether the incoming data stream is processed as

single data rate (SDR) or double data rate (DDR). The allowed values for this attribute are

SDR and DDR. The default value is DDR.

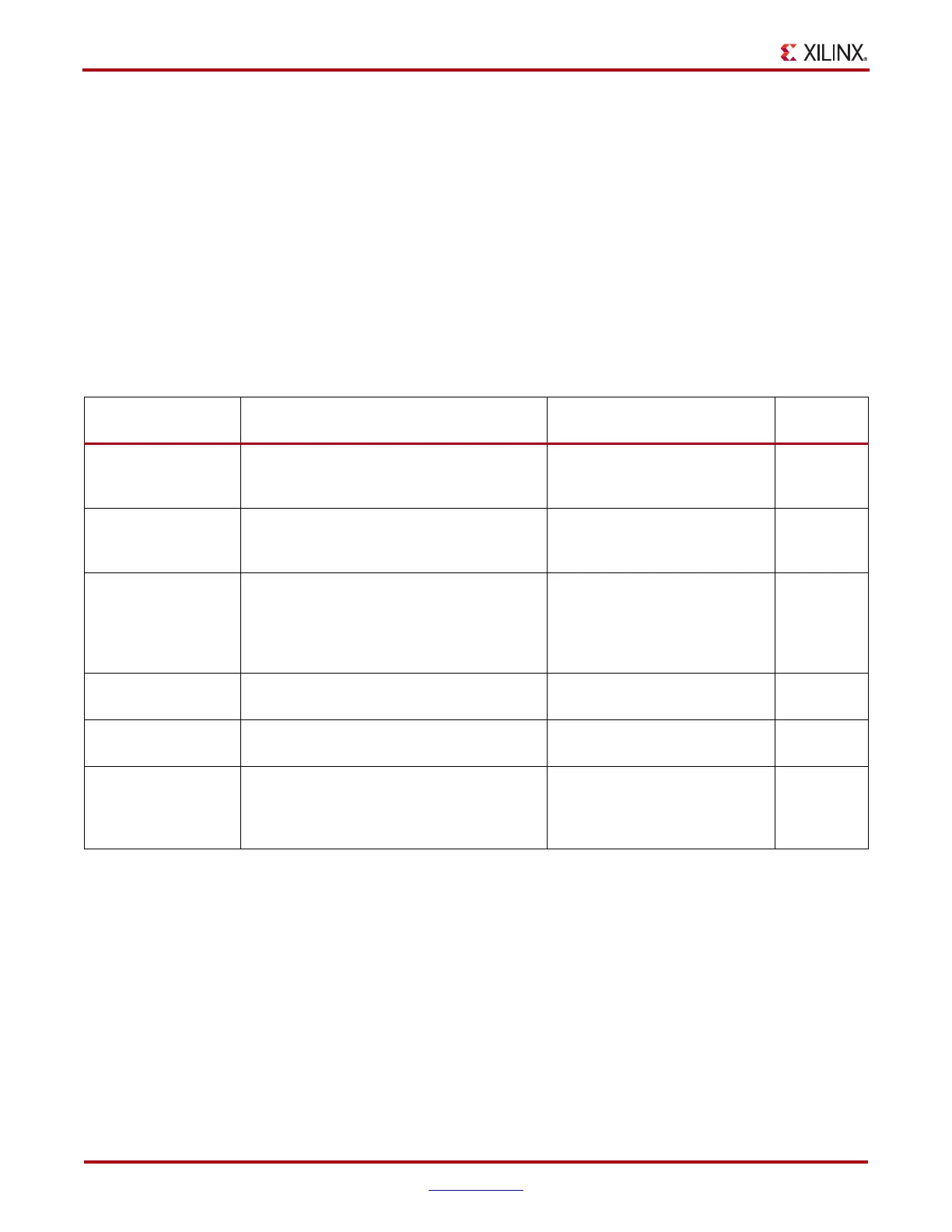

Table 8-2: ISERDES_NODELAY Attributes

Attribute Name Description Value

Default

Value

BITSLIP_ENABLE Allows the user to use the Bitslip submodule

or bypass it. See “BITSLIP_ENABLE

Attribute.”

Boolean: “TRUE” or “FALSE” FALSE

DATA_RATE Enables incoming data stream to be

processed as SDR or DDR data. See

“DATA_RATE Attribute.”

String: “SDR” or “DDR” DDR

DATA_WIDTH Defines the width of the serial-to-parallel

converter. The legal value depends on the

DATA_RATE attribute (SDR or DDR). See

“DATA_WIDTH Attribute.”

Integer: 2, 3, 4, 5, 6, 7, 8, or 10.

If DATA_RATE = DDR, value is

limited to 4, 6, 8, or 10.

If DATA_RATE = SDR, value is

limited to 2, 3, 4, 5, 6, 7, or 8.

4

INTERFACE_TYPE Chooses the ISERDES_NODELAY use

model. See “INTERFACE_TYPE Attribute.”

String: “MEMORY” or

“NETWORKING”

MEMORY

NUM_CE Defines the number of clock enables. See

“NUM_CE Attribute.”

Integer: 1 or 2 2

SERDES_MODE Defines whether the ISERDES_NODELAY

module is a master or slave when using

width expansion. See “SERDES_MODE

Attribute.”

String: “MASTER” or “SLAVE” MASTER

Loading...

Loading...